## I<sup>2</sup>C Communication, 500mA Single Cell Li-Ion Battery Charger with Power

## Path Management, 1mA Termination and <1uA Battery Leakage

### DESCRIPTION

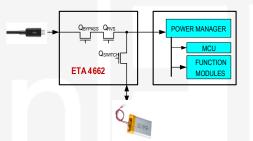

The ETA4662 is a single cell battery charger with power path management function for Li-Ion and Li-Polymer battery. It features pre-charging, fast charging (CC) and constant voltage (CV) charging, end-of charging termination, and auto-recharge, and built-in safe-timer preventing from being over-charged or host running out of control.

The power path management function features a low dropout regulator from the input to the system and a low R<sub>DSON</sub> switch from battery to the system, so it separates the charging current from the system load. This function prioritizes the battery and the system, ensuring the continuous power supply to the system.

Parameters and functions are programmed or selected through an I<sup>2</sup>C compatible serial interface, such as input current limit, charging current, battery regulation voltage, safety timer, battery UVLO. It also features a safe watchdog protection.

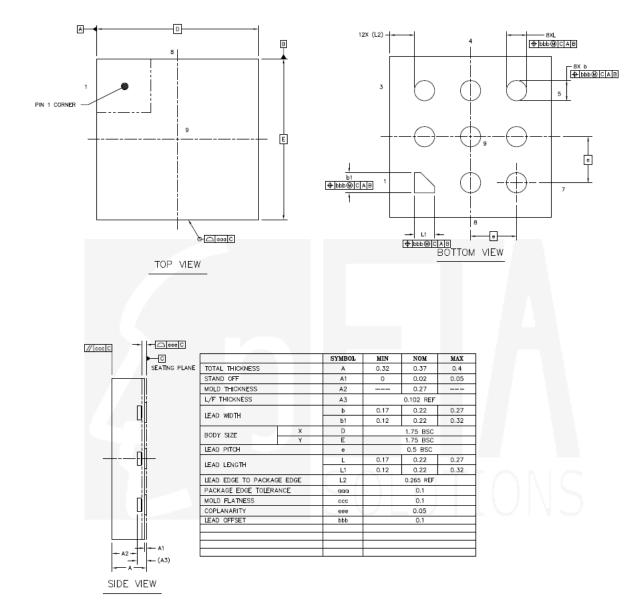

The ETA4662 is available in FCQFN-9L package.

## FEATURES

- Fully Autonomous Charger for Single Cell Li-Ion and Li-Polymer Battery

- 21V Maximum Input Voltage Rating with Over-Voltage Protection

- I<sup>2</sup>C Interface for Setting Charging Parameters and Status Reporting

- Fully Integrated Power Switch and No External

Blocking Diode Required

- Battery Temperature Monitor and Programmable Timer

- Battery or PCB Over-Temperature Protection

- System Reset Function

- Battery Disconnection Function

- Thermal Limiting Regulation on Chip

- FCQFN-9L 1.75x1.75mm

### **APPLICATIONS**

- Wearable Devices

- Smart Watches

- IoT Gadgets

- Smart Handheld Devices

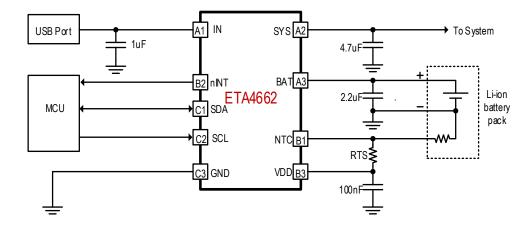

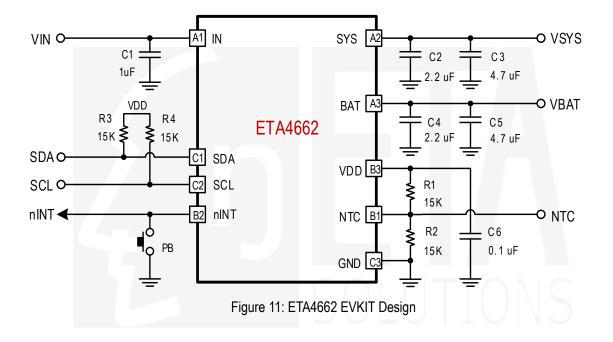

TYPICAL APPLICATION

www.etasolution.com ETA4662\_REV1.8 Empower, Transcend, Achieve!

## ORDERING INFORMATION

PART No. ETA4662FQFJ PACKAGE FCQFN TOP MARK SJY<u>W</u> **Pcs/Reel** 3000

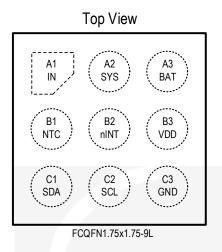

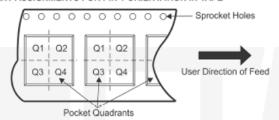

## **PIN CONFIGURATION**

## ABSOLUTE MAXIMUM RATINGS

(Note: Exceeding these limits may damage the device. Exposure to absolute maximum rating conditions for long periods may affect device reliability.)

| IN Pin Voltage to GND                    | 0.3V to 28V        |

|------------------------------------------|--------------------|

| V <sub>IN</sub> to GND Discharge Current | 5mA                |

| Vsys to GND Voltage                      | 0.3V to 5.5V       |

| BAT pin Voltage to GND                   | 1V to 6V           |

| All Other Pins Voltage to GND            |                    |

| VSYS, VBAT to Ground Current             | Internally Limited |

| Operating Temperature Range              | 40°C to 85°C       |

| Storage Temperature Range                | –55°C to 150°C     |

| Thermal Resistance θ <sub>JC</sub>       | ALθ                |

| FCQFN1.75x1.75-9L12                      | °C/W               |

| Lead Temperature (Soldering 10 s         | ecs)260°C          |

| ESD HBM (Human Body Mode)                | 4KV                |

| ESD CDM (Charged Device Mode             | e)1KV              |

## ELECTRICAL CHARACTERISTICS

(V<sub>BAT</sub> = 3.6V, unless otherwise specified. Typical values are at TA =  $25^{\circ}C$ .)

| PARAMETER                                                    | TESTCONDITIONS                           | MIN  | ТҮР  | MAX  | UNIT |

|--------------------------------------------------------------|------------------------------------------|------|------|------|------|

| INPUT AND BATTERY CONDITION                                  | SOLL                                     |      |      | 5    |      |

| Input Under Voltage Lock Out Threshold                       | V <sub>IN</sub> Falling                  | 3.63 | 3.73 | 3.83 | V    |

| V <sub>IN_UVLO</sub> Hysteresis                              | V <sub>IN</sub> Rising                   |      | 170  |      | mV   |

| Input Over Voltage Protection Threshold                      | V <sub>IN</sub> Rising                   | 5.85 | 6    | 6.15 | V    |

| VIN_OVP Hysteresis                                           | V <sub>IN</sub> Falling                  |      | 350  |      | mV   |

| Input Clamp Voltage                                          | Test for having 1mA clamp current.       | 20   |      |      | V    |

| Input Discharge Current                                      | V <sub>IN</sub> = 21V                    |      | 5    |      | mA   |

| $V_{HDRM}$ (Sleep-Mode Entry Threshold, $V_{IN} - V_{BAT}$ ) | VIN Falling vs. VBAT                     |      | 85   |      | mV   |

| Sleep-Mode Exit Hysteresis                                   | VIN Rising vs. VBAT                      | 100  | 130  | 160  | mV   |

| BAT Input Voltage Range                                      |                                          |      |      | 5    | V    |

| Input Detection Deglitch Time                                | For either under-voltage or over-voltage |      | 250  |      | μs   |

| Input Power Detection Time                                   | Time before reporting Power ON or OFF    | 50   | 75   | 100  | ms   |

| PARAMETER                                    | TESTCOND                                                                                                                                                           | ITIONS  | MIN  | TYP  | MAX  | UNIT |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|------|------|------|

|                                              | V <sub>BAT_UVLO</sub> [2:0] = 000                                                                                                                                  |         | 2.3  | 2.4  | 2.5  | V    |

| Battery Under Voltage Lockout Threshold      | V <sub>BAT_UVLO</sub> [2:0] = 100                                                                                                                                  |         | 2.66 | 2.76 | 2.86 | V    |

| (Falling)                                    | VBAT_UVLO[2:0] = 111                                                                                                                                               |         | 2.93 | 3.03 | 3.13 | V    |

| VBAT_UVLO Hysteresis                         | VBAT Falling, VBAT_UVLO=                                                                                                                                           |         | 210  |      | mV   |      |

| Battery Over Voltage Protection<br>Threshold | V <sub>BAT</sub> Rising, higher thar                                                                                                                               | N VTERM |      | 130  |      | mV   |

| V <sub>BAT_OVP</sub> Hysteresis              | V <sub>BAT</sub> Falling                                                                                                                                           |         | 70   |      | mV   |      |

| Battery Over-Voltage Discharge Current       |                                                                                                                                                                    |         | 5    |      | μA   |      |

| SUPPLY CURRENT CONDITION                     |                                                                                                                                                                    |         | •    |      | L    |      |

|                                              | VIN=5.5V, ISYS=0A,                                                                                                                                                 | CEB=0   |      | 250  |      | μA   |

| Input Quiescent Current                      | I <sub>CHG</sub> =0A, EN_HIZ =0                                                                                                                                    | CEB=1   |      | 200  |      | μA   |

| Input Suspend Current                        | VIN=5.5V, VBAT=4.3V, EN                                                                                                                                            | HIZ =1  |      | 70   |      | μA   |

|                                              | V <sub>IN</sub> =5V, CEB=0, V <sub>BAT</sub> =4.3V,<br>Isys=0A, Charge done                                                                                        |         |      | 12   |      | μA   |

|                                              | VIN=GND, CEB=1, V <sub>DD_GATE</sub> =1,<br>BFET_DIS=0,SWITCH_MODE=0,<br>V <sub>BAT</sub> =4.35V, I <sub>SYS</sub> =0A ,disable driving to<br>external NTC circuit |         |      | 5    |      | μA   |

| Battery Quiescent Current                    | V <sub>IN</sub> =GND,SWITCH_MODE=1,<br>V <sub>BAT</sub> =4.35V, I <sub>SYS</sub> =0A ,disable driving to<br>external NTC circuit                                   |         |      | 1    | 5    | μA   |

|                                              | V <sub>IN</sub> =GND, CEB=1, I <sub>SYS</sub> =0A<br>V <sub>BAT</sub> =4.35V,Enable PCB OTP function,<br>not include the external NTC bias                         |         | 1.4  | 8    |      | μA   |

|                                              | V <sub>IN</sub> =GND,CEB=1,V <sub>BAT</sub> =4.35V,I <sub>SYS</sub> =0A,<br>Enable PCB OTP function and Watchdog,<br>not include the external NTC bias             |         |      | 22   |      | μA   |

|                                              | $V_{BAT}$ =4.5V, $V_{IN}$ =V <sub>SYS</sub> =0V,FET_DIS=1, shipping mode                                                                                           |         |      |      | 1    | μA   |

#### POWER PATH MANAGEMENT

|                                 |                  | Vsysreg[3:0]=0000 | 4.15 | 4.2  | 4.25 |   |

|---------------------------------|------------------|-------------------|------|------|------|---|

| Regulated System Output Voltage | $V_{IN} = 5.5V,$ | Vsysreg[3:0]=1001 | 4.60 | 4.65 | 4.70 | V |

| Accuracy                        | Rsys=100Ω        | Vsysreg[3:0]=1111 | 4.90 | 4.95 | 5.00 |   |

| PARAMETER                                                    | TESTCONDITIONS                                                        | MIN  | ТҮР  | MAX  | UNI |  |

|--------------------------------------------------------------|-----------------------------------------------------------------------|------|------|------|-----|--|

| System Over Voltage Protection to<br>Discharger              | Vsys Rising, As Percentage of Vsys_REG                                |      | 10   |      | %   |  |

| Vsys_ovp Hysteresis                                          | Vsys Falling, As Percentage of Vsys_REG                               |      | 5    |      | %   |  |

| Vsys Discharge Resistance                                    | VSYS > VSYS_OVP                                                       |      | 400  |      | Ω   |  |

|                                                              | VINDPM[3:0]=0000                                                      | 3.78 | 3.88 | 3.98 |     |  |

| Input Minimum Voltage Regulation                             | VINDPM[3:0]=1001                                                      | 4.50 | 4.60 | 4.70 | V   |  |

|                                                              | VINDPM[3:0]=1111                                                      | 4.98 | 5.08 | 5.18 |     |  |

|                                                              | IN_ILIM[3:0]=0000 for I <sub>IN_LIM</sub> =50mA                       | 30   | 40   | 50   |     |  |

|                                                              | IN_ILIM[3:0]=0011 for I <sub>IN_LIM</sub> =140mA                      | 125  | 135  | 155  |     |  |

| nput Current Limiting                                        | IN_ILIM[3:0]=1001 for I <sub>IN_LIM</sub> =320mA                      | 200  | 320  | 340  | m/  |  |

|                                                              | IN_ILIM[3:0]=1111 for IINDPM=500mA                                    | 440  | 470  | 500  |     |  |

| IN to SYS Switch On Resistance                               | e V <sub>IN</sub> =4.5V, I <sub>SYS</sub> =100mA                      |      |      |      | mΩ  |  |

| BATFET On Resistance                                         | V <sub>IN</sub> < 2V, V <sub>BAT</sub> =3.5V, I <sub>SYS</sub> =100mA |      | 170  |      | mΩ  |  |

|                                                              | IDISCHG[3:0] = 0001                                                   |      | 400  |      | mA  |  |

| Battery Discharge Current Limit                              | IDISCHG[3:0] = 1001                                                   |      | 2000 |      |     |  |

|                                                              | IDISCHG[3:0] = 1111                                                   |      | 3200 |      |     |  |

| Discharge Short Circuit Limit                                |                                                                       |      | 3.7  |      | A   |  |

| Maximum V <sub>IN</sub> Current to Shutoff                   | V <sub>SYS</sub> falling below V <sub>HSHORT</sub>                    |      | 360  |      | m/  |  |

| VHSHORT(VSYS Short Detection Threshold)                      |                                                                       |      | 1.5  |      | V   |  |

| Delay Before Over Current Cut                                |                                                                       | TT(  | 60   |      | μs  |  |

| Delay Before Retry After Cut                                 | JULU                                                                  | 11   | 800  | 0    | με  |  |

| ldeal Diode Forward Voltage in<br>Supplement Mode            | 10mA Discharge Current                                                |      | 20   |      | m\  |  |

| DYNAMIC POWER MANAGEMENT AND                                 | BATTERY SUPPLEMENT                                                    |      |      |      |     |  |

| SYS Drop For Lowering Charging                               |                                                                       |      | 90   |      | m∖  |  |

| IN Drop For Lowering Charging                                |                                                                       |      | 160  |      | m∖  |  |

| V <sub>SYS</sub> - V <sub>BAT</sub> Drop For Supplement      |                                                                       |      | 30   |      | m∖  |  |

| V <sub>SYS</sub> - V <sub>BAT</sub> Regulation in Supplement |                                                                       |      | 22.5 |      | m\  |  |

| V <sub>SYS</sub> - V <sub>BAT</sub> Drop For Exit Supplement |                                                                       |      | 20   |      | m\  |  |

| SHIPPING MODE AND BATFET RESET                               |                                                                       |      |      |      |     |  |

| Enter Shipping Mode Deglitch Time                            | FET_DIS is set from 0 to 1,<br>EN_SHIPPING_DGL[1:0]=00                |      | 1    |      | s   |  |

| Exit Shipping Mode by Push Button                            | nINT is pulled low                                                    |      | 2    |      | s   |  |

| PARAMETER                                                       | TESTCONDITIONS                       | MIN   | ТҮР   | МАХ   | UNIT |  |

|-----------------------------------------------------------------|--------------------------------------|-------|-------|-------|------|--|

| Exit Shipping Mode by V <sub>IN</sub> Plug-in                   |                                      |       | 68    |       | ms   |  |

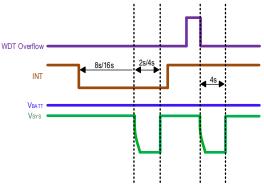

| Deast by alNT                                                   | trst_dgl[1:0] = 00                   |       | 8     |       | s    |  |

| Reset by nINT                                                   | trst_dgl[1:0] = 10                   |       | 16    |       | 3    |  |

|                                                                 | trst_dgl [0] = 0                     |       | 2     |       | 6    |  |

| BATFET Off Lasting Time                                         | t <sub>RST_DGL [0]</sub> = 1         |       | 4     |       | S    |  |

| BATTERY CHARGER                                                 |                                      |       |       |       |      |  |

|                                                                 | VTERM[5:0] = 000000                  | 3.582 | 3.60  | 3.618 |      |  |

| Battery Charge Termination Voltage                              | VTERM[5:0] = 101000                  | 4.179 | 4.200 | 4.221 |      |  |

| Regulation (Aging and pre-condition drift included in 0°C~50°C) | VTERM[5:0] = 110010                  | 4.358 | 4.380 | 4.402 | V    |  |

|                                                                 | VTERM[5:0] = 111110                  | 4.522 | 4.545 | 4.568 |      |  |

|                                                                 | ICHRG[5:0]=000000                    |       | 8     |       |      |  |

| Fast Charge Current                                             | ICHRG[5:0]=001011                    | 91    | 96    | 101   | mA   |  |

|                                                                 | ICHRG[5:0]=100000                    | 251   | 264   | 277   |      |  |

|                                                                 | ICHRG[5:0]=111000                    | 433   | 456   | 479   |      |  |

| Pre-Charge Current                                              | IPRE = ITERM                         | 1     |       | 31    | mA   |  |

|                                                                 | ITERM[3:0]=0000                      |       | 1     |       |      |  |

|                                                                 | ITERM[3:0]=0001                      | 2.7   | 3     | 3.3   | mA   |  |

| Charge Termination Current Threshold                            | ITERM[3:0]=0101                      | 10    | 11    | 12    |      |  |

|                                                                 | ITERM[3:0]=1111                      | 28    | 31    | 34    |      |  |

| Precondition to Fast Charge Threshold                           | Rising, VPRECOND = 1                 | 2.9   | 3.0   | 3.1   | V    |  |

| Precondition to Fast Charge Hysteresis                          | Falling                              | 17    | 90    | C.    | mV   |  |

|                                                                 | Below V <sub>TERM</sub> , VRECHG = 0 | 70    | 100   | 130   |      |  |

| Auto Recharge Voltage Threshold                                 | Below V <sub>TERM</sub> , VRECHG = 1 | 160   | 200   | 240   | mV   |  |

| Termination Deglitch Time                                       |                                      |       | 200   |       | ms   |  |

| Battery Auto-Recharge Deglitch Time                             |                                      |       | 200   |       | ms   |  |

| Fast Charge Safety Timer                                        | CHG_TMR [1:0]=01, EN_TIMER = 1       |       | 5     |       | hrs  |  |

| THERMAL PROTECTION                                              |                                      |       |       |       |      |  |

| Junction Temperature Regulation Range                           | I <sup>2</sup> C programmable range  | 60    |       | 120   | °C   |  |

| lunction Tomperature Deputation                                 | TJ_REG[1:0] =11 for Thermal          |       | 100   |       | *0   |  |

| Junction Temperature Regulation                                 | Regulation=120°C                     |       |       | °C    |      |  |

| Thermal Shutdown Threshold                                      |                                      |       | 150   |       | °C   |  |

| Thermal Shutdown Hysteresis                                     |                                      |       | 20    |       | °C   |  |

| PARAMETER                                     | TESTCONDITIONS                                               | MIN  | ТҮР | MAX | UNIT |

|-----------------------------------------------|--------------------------------------------------------------|------|-----|-----|------|

| NTC Pin Output Current                        | V <sub>NTC</sub> = 3V                                        | -100 | 0   | 100 | nA   |

| NTC Cold Temperature Threshold                | $V_{\text{NTC}}$ Rising , As percentage of $V_{\text{LDO}}$  | 63   | 65  | 67  | %    |

| NTC Cold Temperature Hysteresis               | $V_{\text{NTC}}$ Falling , As percentage of $V_{\text{LDO}}$ |      | 30  |     | mV   |

| NTC Hot Temperature Threshold                 | $V_{\text{NTC}}$ Falling , As percentage of $V_{\text{LDO}}$ | 31   | 33  | 35  | %    |

| NTC Hot Temperature Hysteresis                | $V_{\text{NTC}}$ Rising , As percentage of $V_{\text{LDO}}$  |      | 70  |     | mV   |

| NTC Hot Temperature Threshold for PCB<br>OTP  | $V_{\text{NTC}}$ Falling , As percentage of $V_{\text{LDO}}$ | 30   | 32  | 34  | %    |

| NTC Hot Temperature Hysteresis for PCB<br>OTP | $V_{\text{NTC}}$ Rising , As percentage of $V_{\text{LDO}}$  |      | 85  |     | mV   |

| LOGIC IO PIN SPECIFICATION, nINT, SC          | L, SDA                                                       |      |     |     |      |

| Input Low Logic Voltage Threshold             | Falling                                                      |      |     | 0.4 | V    |

| Input High Logic Voltage Threshold            | Rising                                                       | 1.3  |     |     | V    |

| Output Low Level                              | I <sub>SINK</sub> = 5mA                                      |      |     | 0.4 | V    |

| I <sup>2</sup> C SPECIFICATION                |                                                              |      |     |     |      |

| I <sup>2</sup> C Clock Frequency              |                                                              |      |     | 400 | KHz  |

| WATCHDOG                                      |                                                              |      |     |     |      |

| Watchdog Timer                                | WATCHDOG[1:0]=11                                             |      | 160 |     | S    |

NOTE: For lowering the bias current in the chip, and also to avoid biasing external circuit with output of nINT, the logic high level of the nINT should be a buffered level of an internal reference in range of 1.8~2.5V, at a roughly regulated voltage level.

## PIN DESCRIPTION

| PIN # | PIN NAME | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1    | IN       | Р    | Input Power Pin. Place a ceramic capacitor from IN pin to GND as close as possible to this device.                                                                                                                                                                                                                                                                                                                     |

| A2    | SYS      | Р    | System Power Supply. Place a ceramic capacitor from SYS pin to GND as close as possible to this device.                                                                                                                                                                                                                                                                                                                |

| A3    | BAT      | Р    | Battery Pin. Place a ceramic capacitor from BAT pin to GND as close as possible to IC.                                                                                                                                                                                                                                                                                                                                 |

| B1    | NTC      | AIO  | Battery Temperature Qualification Input Pin. Connect a negative temperature coefficient thermistor. Program temperature window with a resistor divider from VDD to NTC to GND. Charge suspends when either NTC pin is out of range. When NTC pin is not used, connect a 10-k $\Omega$ resistor from VDD to NTC and connect a 10-k $\Omega$ resistor from NTC to GND. Or NTC can be used like charge disable input pin. |

| B2    | nINT     | AIO  | Interrupt Output and Battery FET Reset Input pin. The nINT pin sends charging status and fault notification to the host.<br>This pin is also used to reset the system from the battery. Refer to " <i>Interrupt to Host (nINT)</i> " and " <i>Battery Disconnection Function</i> " sections for detail information.                                                                                                    |

| B3    | VDD      | Р    | Internal Control Power Supply Pin. Connect a 0.1µF ceramic cap from this pin to GND.                                                                                                                                                                                                                                                                                                                                   |

| C1    | SDA      | DIO  | I <sup>2</sup> C Interface Data. Connect SDA pin to the logic rail through a $10k\Omega$ resistor.                                                                                                                                                                                                                                                                                                                     |

| C2    | SCL      | DI   | I <sup>2</sup> C Interface Clock. Connect SCL pin to the logic rail through a $10k\Omega$ resistor.                                                                                                                                                                                                                                                                                                                    |

| C3    | GND      | Р    |                                                                                                                                                                                                                                                                                                                                                                                                                        |

NOTE: AIO = Analog Input /Output; DI = Digital Input; DO = Digital Output; DIO = Digital Input /Output; P = Power.

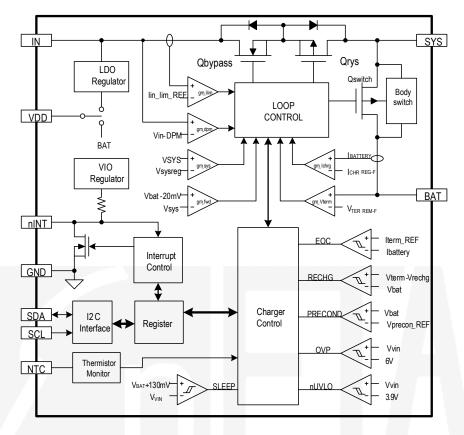

## FUNCTIONAL BLOCK DIAGRAM

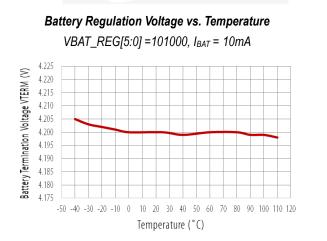

## TYPICAL PERFORMANCE CHARACTERISTICS

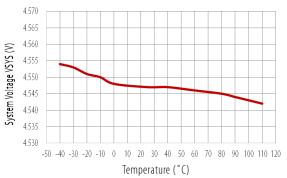

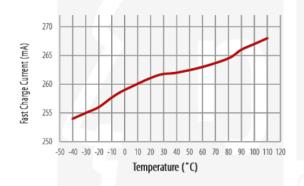

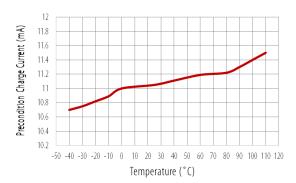

(V<sub>IN</sub> =5V, V<sub>BAT</sub>=4.2V unless otherwise specified. Typical values are at TA = 25°C.)

System Regulation Voltage vs. Temperature VSYS\_REG[3:0] =0111, I<sub>VSYS</sub> = 10mA

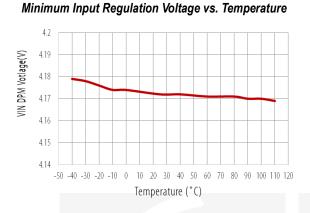

(V<sub>IN</sub> =5V, V<sub>BAT</sub>=4.2V unless otherwise specified. Typical values are at TA = 25°C.)

Fast Charge Current vs. Temperature

Precondition Charge Current vs. Temperature

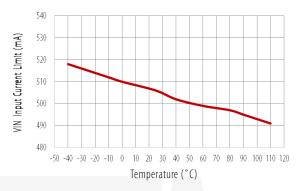

Input Current Limit Regulation vs. Temperature

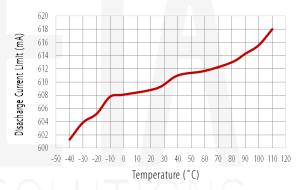

Discharge Current Limit vs. Temperature

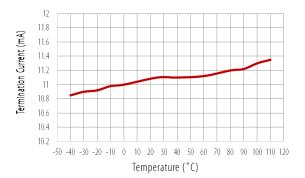

Termination Current vs. Temperature

(V<sub>IN</sub> =5V, V<sub>BAT</sub>=4.2V unless otherwise specified. Typical values are at TA = 25°C.)

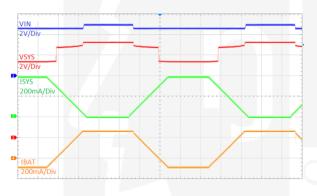

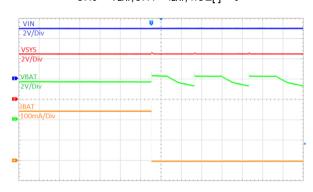

Minimum Input voltage regulation based PPM CH1 = V<sub>IN</sub>,CH2 = V<sub>SYS</sub>,CH3 = I<sub>SYS</sub>,CH4 = I<sub>BAT</sub>

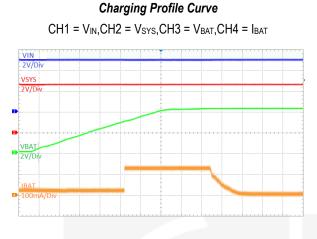

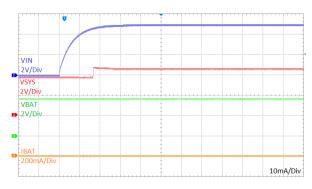

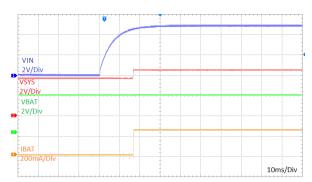

VIN Plug-in, Charge Start-Up Waveform  $CH1 = V_{IN}, CH2 = V_{SYS},$  $CH3 = V_{BAT}, CH4 = I_{BAT}, nCE[] = 1$

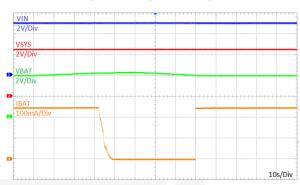

**Recharging Profile Curve** CH1 = V<sub>IN</sub>,CH2 = V<sub>SYS</sub>,CH3 = V<sub>BAT</sub>,CH4 = I<sub>BAT</sub>

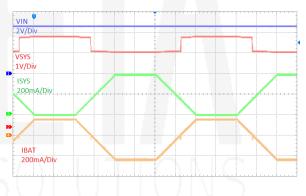

Minimum Input voltage regulation based PPM CH1 = V<sub>IN</sub>,CH2 = V<sub>SYS</sub>,CH3 = I<sub>SYS</sub>,CH4 = I<sub>BAT</sub>

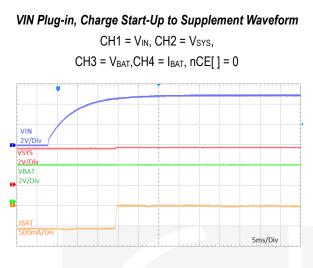

VIN Plug-in, Charge Start-Up Waveform  $CH1 = V_{IN}, CH2 = V_{SYS},$  $CH3 = V_{BAT}, CH4 = I_{BAT}, nCE[] = 0$

(VIN =5V, VBAT=4.2V unless otherwise specified. Typical values are at TA = 25°C.)

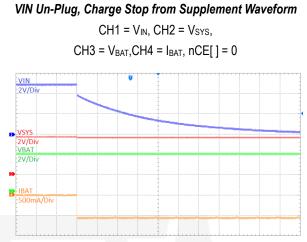

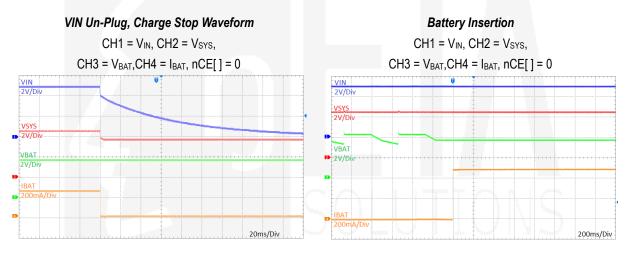

Battery Removal CH1 = V<sub>VIN</sub>, CH2 = V<sub>SYS</sub>, CH3 = V<sub>BAT</sub>,CH4 = I<sub>BAT</sub>, nCE[] = 0

www.etasolution.com ETA4662\_REV1.8

(V<sub>IN</sub> =5V, V<sub>BAT</sub>=4.2V unless otherwise specified. Typical values are at TA =  $25^{\circ}$ C.)

## **OPERATION**

### **General Description**

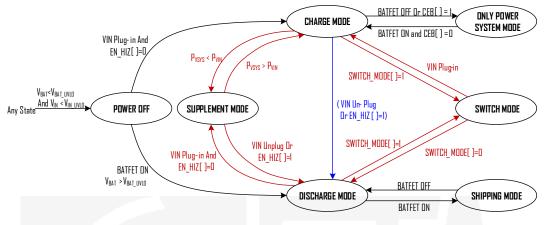

The ETA4662 is a single cell battery charger with power path management function for Li-Ion and Li-Polymer battery. It features pre-charging, fast charging (CC) and constant voltage (CV) charging, end-of charging termination, and auto-recharge, and built-in safe-timer preventing from being over-charged or host running out of control.

A bypass FET between VIN and SYS pin, and a battery switch FET between SYS and BAT pin is integrated for providing to complete power path management. System load is prior in getting power from the input or is switched to battery power when the input is weak or removed. Power to the battery is regulated by the battery switch FET during charging, while the input voltage, input current, voltage to system load, chip temperature and sensed external temperature are kept in priority.

错误!未找到引用源。1: shows the power path and key circuit blocks in the ETA4662, where the Q<sub>BYPASS</sub> regulates voltage to the system load and to the circuit for charging, the Q<sub>RVS</sub> prevents reverse leakage from the SYS node to VIN node and the Q<sub>SWITCH</sub> regulates for charging or gates the discharging from the BAT node to SYS node. The charging circuit and the discharging circuit have their own UVLO and bias, and the common circuit is powered by the higher voltage of the IN node or SYS node. The I/F is ready whenever any power is available.

The power fed to the SYS pin is recycled when watchdog times out, the host does not response to IN power input(when watchdog is forced on) or BFET\_RESET[1] is set 1, to clear the running environment before system program upgrade or

release from locked situations.

Figure 1: Power Path Management Structure

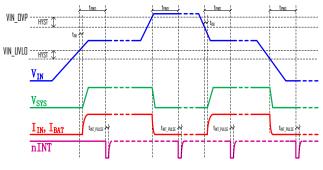

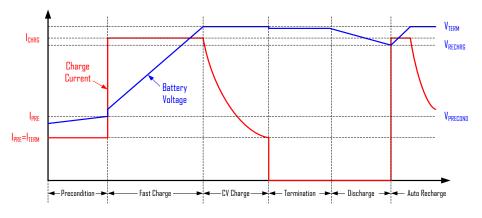

### Input Detection

The device monitors the input at the VIN node. When the input is within the normal range certified by the UVLO circuit and OVP circuit for more than  $t_{INI}$  the charge circuit starts. The circuit stops or turns into OVP cut off instantly when the input voltage is lower than VIN\_UVLO or is higher than VIN\_OVLO, that the Q<sub>BYPASS</sub> and Q<sub>RVS</sub> are turned open.

错误!未找到引用源。**2**: shows the timings relative to the input detection. The input state is certified after t<sub>INI</sub> and stays for over t<sub>PWD</sub>, the device outputs a pulse through the nINT. The nINT is internally pulled up to an unregulated reference voltage unless the battery is set into disconnected state. The nINT asserts pulse whenever an effective input change is certified, while the changes occurring within t<sub>PWM</sub> do not assert pulse.

The watchdog timer register is set 01 once the valid input is detected and when a nINT pulse is asserted, which resumes its original setting when any writing to this device occurs. If the host does not reset the watchdog, power to the host is recycled when watchdog runs time out.

## Power Path Management

When the input is available ( $V_{IN} > V_{IN}_{UVLO}$ ,  $V_{IN} - V_{SYS} > V_{HDRM}$ ), the device intends to power the system load with input by regulating the input voltage to  $V_{SYS\_REG}$  ( $V_{SYS}$  is decided by the input voltage, input current limit and battery voltage in reality).  $V_{SYS\_REG}$  is programmed through REG07[3:0], The  $Q_{BYPASS}$  and  $Q_{SWITCH}$  are also manipulated by corresponding register bits, as showed in the 错误!未找到引用源。.

#### Table 1. FET Control by I<sup>2</sup>C

| FETs                  | EN_HIZ = 1 | CEB = 1 |

|-----------------------|------------|---------|

| QBYPASS               | OFF        | Х       |

| Qswiтcн (Charging)    | Х          | OFF     |

| Qswitch (Discharging) | X          | Х       |

NOTE: X = Don't Care.

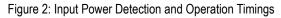

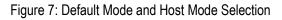

### Battery Charge Profile

The charging profile managed by the device is as shown in *错误*!*未找到引用源。***e3**, which is segmented as following phases:

Pre-charge: If the battery voltage is less than the pre-charging threshold  $V_{BAT_PRE}$ , it charges the battery with pre-charging current, which shares the same value of the termination current programmed ITERM[3:0].

Constant-Current Charge: When battery voltage is higher than V<sub>BAT\_PRE</sub>, and is less than V<sub>BAT\_REG</sub>, it is charged with constant current that is programmed ICC[5:0] and a bit to choose scale of the current, the CC\_FINE in REGOA.

Constant-Voltage Charge: When the battery voltage rises close to the battery voltage VBAT\_REG[5:0], the charge current

begins to decreases until the termination situation is identified.

When the charging termination function EN\_TERM set via REG05 D[4] = 1, the charge cycle is considered as completed when following termination condition is identified: 1. The charge current  $I_{CHG}$  reaches the termination current threshold  $I_{TERM}$ , for over trence trence trence the transmission of time if this function is enabled set via the REG05[3].

The charge status is updated to charge done once the termination condition is identified. The charge current will be terminated when termination conditions are met if TERM\_TMR is not set via REG05[0]; otherwise the charge current keeps tapering off when it is set by REG05[0]=1.

During the whole charging process, the actual charge current may be less than the register setting due to other loop regulations like dynamic power management (DPM) regulation (input voltage, input current), or thermal regulation.

A new charge cycle starts when any one of the following conditions are valid:

- The input power is recycled

- Battery charging is enabled by I<sup>2</sup>C

- Auto-recharge kicks in.

Under the following conditions:

No thermistor fault at NTC.

- No safety timer fault.

- No battery over voltage event.

- The Qswitch is not forced to turn off

Figure 3: Battery Charge Profile

## Battery Over-Voltage Protection

This device is designed with a built-in battery over-voltage limit about VBAT\_OVP higher than the VBAT\_REG. When the battery over-voltage event occurs, the device immediately suspends the charging and asserts a fault. A discharging path is turned on when the battery OVP keeps.

## Input Current and Input Voltage Based Power Path Management

To meet the input source (USB usually) maximum current limit specification, the IC features the input current based power management by continuously monitoring the input current. The total input current limit can be programmed via the I2C to prevent the input source from over-loaded.

If the preset input current limit is higher than the rating of the input source, the back-up input voltage based power management also works to prevent the input source from being over-loaded. Either the input current limit or the input voltage limit is reached, the Q<sub>BYPASS</sub> between IN and SYS pin will be regulated so that the total input power will be limited. As a result the system voltage drops, once the system declines to minimum value of the VSYS\_REG - DVSYS\_LOW and VIN - DVIN\_LOW, the charge current will be reduced to prevent the system voltage from dropping further.

The voltage based dynamic power management (DPM) will regulate the input voltage to VIN\_MIN when the load is over the input power capacity.

The VIN\_MIN set via I<sup>2</sup>C should be at least 250mV higher than VBAT\_REG to make sure the stable operation of the regulator.

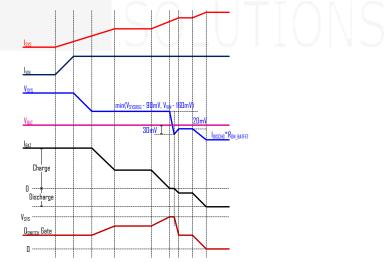

## **Battery Supplement Mode**

As mentioned above, the charge current is reduced to keep the input current or input voltage in regulation when DPM happens. If the charge current is reduced to zero and the input source is still overloaded due to heavy system load, the system voltage starts to decrease. Once the system voltage falls V<sub>SYS-BAT\_LOW</sub> below the battery voltage, the device enters battery supplement mode and the ideal diode mode will be enabled. The Qswitch is regulated to maintain the V<sub>BAT</sub>-V<sub>SYS</sub> at V<sub>SYS-BAT\_REG</sub> when I<sub>DSCHG</sub> (supplement current) × R<sub>ON\_BAT</sub> is lower than V<sub>SYS-BAT\_REG</sub>, in the case the I<sub>DSCHG</sub> x R<sub>ON\_BAT</sub> is higher than V<sub>SYS-BAT\_REG</sub>, the Qswitch is fully turned on to keep ideal forward voltage. During system load decreasing, once V<sub>SYS</sub> is higher than V<sub>BAT</sub> + V<sub>SYS-BAT\_HIGH</sub>, the ideal diode mode will be disabled. 错误!未找到引用源。 shows the dynamic power management and battery supplement mode operation profile.

When VIN is not available, the device operates in discharge mode, the QSWITCH is always fully on to reduce the loss.

### **Battery Regulation Voltage**

The battery voltage for the constant voltage regulation phase is  $V_{BAT_{REG}}$ . When battery is float, the BAT pin voltage varies between  $V_{BAT_{REG}}$  -  $V_{RECH}$  and  $V_{BAT_{REG}}$ .

## Thermal Regulation and Shutdown

The device continuously monitors the internal junction temperature to maximize power delivery and avoid overheating the chip. When the internal junction temperature reaches preset limit of  $T_{J_REG}$ , the device starts to reduce the charge current to prevent higher power dissipation. The programmable thermal regulation thresholds help system design to meet the thermal requirement in different applications. The junction temperature regulation threshold can be set via TJ\_REG[1:0].

When the junction temperature reaches  $T_{J\_SHDN}$  that is slightly higher than most high programmable thermal regulation temperature threshold, both the  $Q_{BYPASS}$  and  $Q_{SWITCH}$  are turned off.

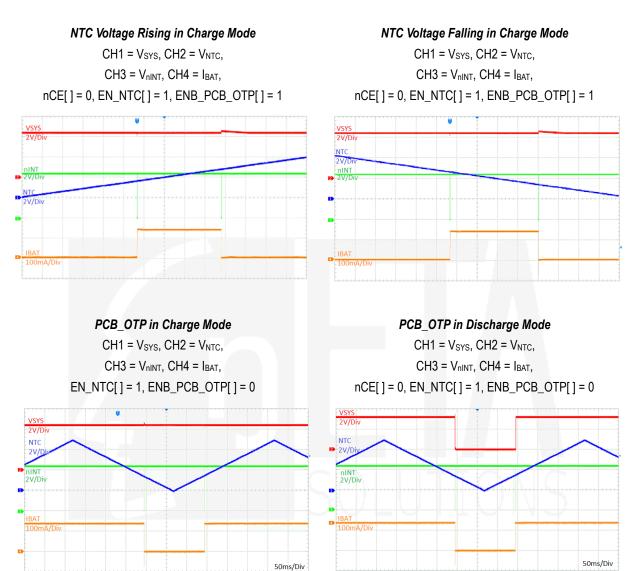

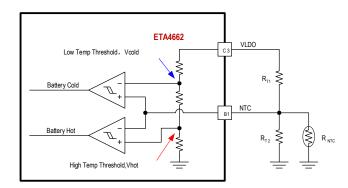

## NTC Sensing and VDD Gating

The NTC pin allows the device to sense the battery temperature using the thermistor usually available in the battery pack to ensure a safe operating environment of the chip. A resistor with appropriate value should be connected from VDD pin to NTC pin and the thermistor is connected from NTC pin to ground. The voltage on NTC pin is determined by the resistor divider whose divide ratio depends on temperature. The device internally sets a pre-determined upper and lower bound of the divide ratio for NTC cold and NTC hot.

In ETA4662, I<sup>2</sup>C default setting is the PCB OTP; user can change the function through I<sup>2</sup>C:

|          |     | •        |           |

|----------|-----|----------|-----------|

| Table 2. | NTC | Function | Selection |

| I <sup>2</sup> C CON | TROL       | FUNCTION |

|----------------------|------------|----------|

| EN_NTC               | EN_PCB OTP | FUNCTION |

| 0                    | X          | Disable  |

| 1                    | 1          | NTC      |

| 1                    | 0          | PCB OTP  |

The VDD powering from battery when not powered by the supply applied on the IN pin is gated via setting a register bit DIS\_VDD.

When PCB OTP is selected, if the NTC pin voltage is lower than the NTC hot threshold, both the  $Q_{BYPASS}$  and  $Q_{SWITCH}$  are off. The PCB OTP fault also will set the NTC\_FAULT status to 1 to show the fault. The operation will resume once the NTC pin voltage is higher than the NTC hot threshold.

NTC function only works in charge mode. Once NTC pin voltage falls out of this divide ratio which means the temperature is outside the safe operating range, the device will stop the charging and report it on status bits. Charging will automatically resume after the temperature falls back into the safe range.

### Safety Timer

The device provides both the pre-charge and charge safety timer to prevent extended charging cycle due to abnormal battery conditions. The safety timer is 1hr when battery voltage is lower than  $V_{BAT\_PRE}$ . The charge safety timer starts when the battery enters constant-current or constant-voltage charge. The user can program charge safety timer through I<sup>2</sup>C. The safety timer

feature can be disabled via I<sup>2</sup>C.

The following actions restart the safety timer:

- A new charge cycle is kicked in.

- Write REG01[3] from 1 to 0 (charge enable)

- Write REG05[3] from 0 to 1 (safety timer enable)

- Write REG02[7] from 0 to 1 (software reset)

- Write REG0A[4] from 0 to 1 (software power recycle)

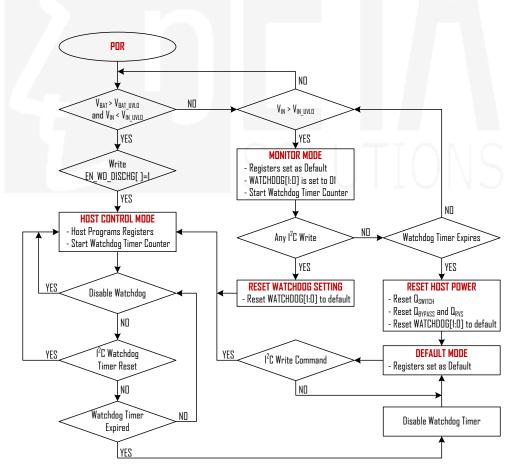

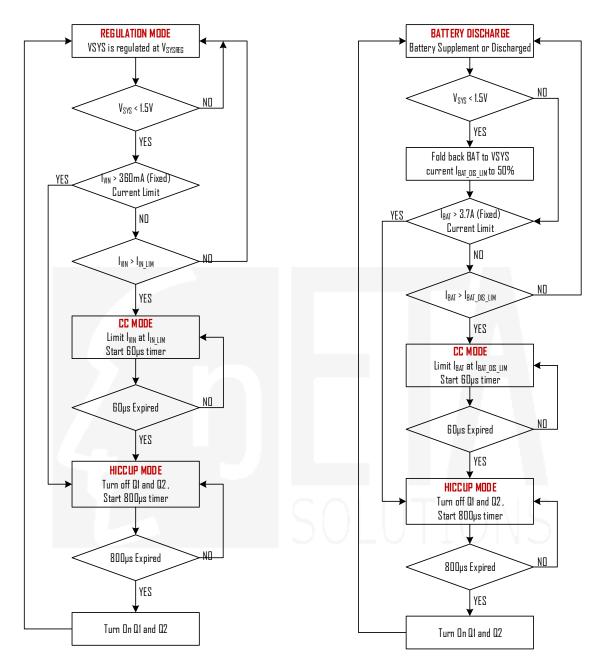

### Host Mode and Default Mode

Upon power on reset, the device starts in the watchdog timer expiration state, or default mode. All the registers are in the default settings, when the EN\_HIZ = 0, CEB = 1, power input and battery discharge are enabled.

Watchdog timer works in both charge and discharge mode. When the watchdog timer runs time out, the power to load system recycles by cutting off the  $Q_{\text{SWITCH}}$  and  $Q_{\text{BYPASS}}$  for the default of  $t_{\text{RST}_{\text{DUR}}}$  and all the registers in this device reset to the default value.

And to save the quiescent current during discharge mode, the watchdog timer can be turned off during discharge mode by set the EN\_WD\_DISCHG bit to 0.

Any write to the device transits it to host mode. If the watchdog timer (WATCHDOG[1:0]) is not disabled, the host has to reset the watchdog timer regularly by writing 1 to REG02 WD\_RST bit before the watchdog timer expires to keep the device in host mode. Once the watchdog timer expires, the device goes back into default mode. The watchdog timer limit can also be programmed or disabled by host control.

When the WATCHDOG[1:0] is set to 00, then the watchdog timer is disabled under both charge mode and discharge mode no matter EN\_WD\_DISCHG status is.

The operation could also be turned to default mode when one of the following conditions are valid:

- Refresh input without battery

- Re-insert battery with no VIN

- Register reset REG\_RST bit is set 1

### Battery Discharge Function

If battery is connected and the input source is missing, the  $Q_{SWITCH}$  is fully on when VBAT is above the VBAT\_UVLO threshold. The low Ron  $Q_{SWITCH}$  minimizes the conduction loss during discharge. The quiescent current of the device is as low as 6µA in this mode. By setting REG0A[3] = 1, the  $Q_{SWITCH}$  keeps on with sensing circuit off, to further reduce the quiescent current to below 1µA. The low on-resistance and low quiescent current help extend the running time.

### **Over-Discharge Current Protection**

The over-discharge current protection is effective in discharge mode and supplement mode. Once the IBAT exceeds discharge current limit programmed through the REG03[7:4], the  $Q_{SWITCH}$  cuts off after  $t_{DSCHG_CUT}$  and the device resumes conducting after  $t_{RETRY}$ . Besides, if the discharge current goes high to hit IDSCHG\_S, the  $Q_{SWITCH}$  cuts off instantly.

When the battery voltage falls below VBAT\_UVLO programmed through the REG01[2:0], the Q<sub>SWITCH</sub> cuts off to prevent over discharge.

When REG0A[3] is set 1, the Q<sub>SWITCH</sub> is forced on and the over-discharge is not sensed during battery discharge. The REG0A[3] is reset 0 when effective power input to the IN applied. If the REG0A[3] is set when only the power input applied, attaching to detaching the battery does not make any change to the status.

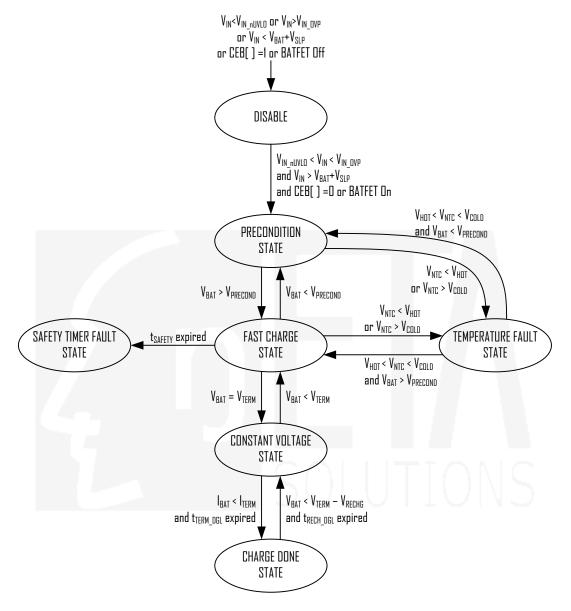

### System Short Circuit Protection

When system short circuit occurs, the Q<sub>SWITCH</sub> cuts the BAT to SYS path and the Q<sub>BYPASS</sub> limits the current input through the IN to SYS path. If the system short circuit remains, the die temperature goes high to cause thermal shut down.

The ETA4662 features V<sub>SYS</sub> node short circuit protection for both V<sub>IN</sub> to V<sub>SYS</sub> path and BAT to VSYS path.

- VIN to V<sub>SYS</sub> path: The ETA4662 starts activate hard short protection after V<sub>SYS</sub> goes greater than 1.5V once. This means the IC allows to start-up with full current limit. Once this condition occurs, if V<sub>SYS</sub> falls below 1.5V, and I<sub>IN</sub> is found over the protection threshold, Q<sub>SWITCH</sub>, Q<sub>BYPASS</sub> and Q<sub>RVS</sub> are turned off immediately. And the operation of the IC goes into the hiccup mode. Beside hard short protection, at any time V<sub>SYS</sub> is lower than 1.5V, while the setting input current limit is reached, I<sub>IN</sub> is regulated at I<sub>IN\_LIM</sub> the hiccup mode also starts after a 60µs delay. The interval of the hiccup mode is 800us.

- BATT to SYS path: Once I<sub>BAT</sub> is found over the 3.7A protection threshold, both the LDO FET and the BATT FET are turned off immediately and the operation of the IC goes into the hiccup mode. Besides, while the battery discharge current limit threshold is reached, the hiccup mode also starts after a 60µs delay. The interval of the hiccup mode is 800us.

- Particularly, if the system short circuit happens when both input and battery are present, the protection mechanism of both paths will work, the faster one dominates the hiccup operation.

### Interrupt to Host (INT)

This device also has an alert mechanism which can output an interrupt signal via nINT pin to notify the system on the operation by outputting low for t<sub>INT\_PULSE</sub>. Any of the events listed below triggers the nINT output.

- Good input source detected

- UVLO or input over voltage detected

- Charge completed

- Charging status change

Any fault recorded in REG09 (input fault, thermal fault, safety timer fault, battery OVP fault, NTC fault) and in REG08[7] occurs.

When any fault occurs, this device sends out nINT pulse and latches the fault state in register bits correspondingly. After the device quit the fault state, the fault bit could be released to 0 after the host reads. The NTC fault is not latched and always reports the current thermistor conditions.

The INT signal can be masked when the corresponding control bit is set, which means, even the event which causes the INT signal happened, user can just keep the nINT high when the INT signal is not acceptable in the application, via setting the INT control bit in REG06[4:0].

The nINT is pulled up to an unregulated low voltage that is not high enough to most logic circuit (in the circuit the device loads), to avoid unexpected creeping powering and leakage during power recycling and in shipping mode; the nINT is pulled up to a high voltage in other states. Both the low voltage and high voltage are internally generated and pull up is weak and could be over-driven externally.

### Battery Disconnection Function

In the application that the battery is not removable, it's essential to disconnect the battery from the system for shipping mode in stock or to allow the recycle of the system power during the application. ETA4662 provides both shipping mode (shown in Table 3) and system power recycling for different applications.

|                                      | ENTER SHIPPING MODE                                        | EXIT SHIPPING MODE |               |  |

|--------------------------------------|------------------------------------------------------------|--------------------|---------------|--|

| ITEMS                                | FET_DIS = 1 nINT Pin<br>H to L for 2s                      |                    | VIN Plug In   |  |

| LDO FET                              | X<br>(To disable LDO FET (VIN to<br>VSYS), set EN_HIZ[]=1) | Х                  | ON            |  |

| Qswiтсн<br>(Charging)                | OFF                                                        | ON                 | ON (2s Later) |  |

| Q <sub>swiтсн</sub><br>(Discharging) | OFF                                                        | ON                 | ON (2s Later) |  |

#### Table 3. Shipping Mode Control

NOTE: x = Don't Care.

The FET\_DIS bitfor battery disconnection control. If this bit is set to 1, it enters shipping mode after a delay time, which can be programmed by EN\_SHIP\_DGL[1:0], the Q<sub>SWITCH</sub> turns off and the FET\_DIS bit refresh to 0 after the Q<sub>SWITCH</sub> is off. Pulling down nINT pin or VIN is detected, the device wakes up from shipping mode.

This device can also reuse nINT pin or watchdog overflow signal to cut off the path from battery to system under the condition need to recycle the system power. Once the logic at nINT pin set to low for more than  $t_{INT_OFF}$  which can be programmed via  $t_{RST_DGL}$  or watchdog time is overflow, the battery is disconnected from the system by turning off the QswITCH and QBYPASS, the off state lasts for  $t_{INT_ON}$  which can be programmed via  $t_{RST_DUR}$ , then the QswITCH and QBYPASS will be automatically turned on and system is powered again. During the off period, the nINT pin is biased to a lower voltage.

The waveforms of power recycling are shown in 错误!未找到引用源。5

Figure 5. Power Recycling Waveforms

## **OPERATION DIAGRAM**

#### Main State Machine

Figure 6: State Machine Conversion

### HOST Control Flow Chart

## **Charger Flow Chart**

Figure 8: Charger Flow Chart

## System Short Circuit Protection

Figure 9: System Short Circuit Protection

## APPLICATION INFORMATION

### Resistor Choose for NTC Sensor for Battery Temperature Monitor

NTC pin uses a resistor divider from input source (VDD) to sense the battery temperature. The two resistors RT1 and RT2 allow the high temperature limit and low temperature limit to be programmed independently, as shown in Figure. In other word, this device can fit most type of NTC resistor and different temperature operation range requirement with the two extra resistors.

For a given NTC thermistor, RT1 and RT2 values depend on the type of the NTC resistor and can be calculated with following equations:

$$R_{T2} = \frac{(V_{COLD} - V_{HOT}) \times R_{NTCH} \times R_{NTCL}}{(V_{HOT} - V_{COLD} \times V_{HOT}) \times R_{NTCL} - (V_{COLD} - V_{COLD} \times V_{HOT}) \times R_{NTCH}}$$

$$R_{T1} = \frac{1 - V_{COLD}}{V_{COLD}} \times \frac{R_{T2} \times R_{NTCL}}{R_{T2} + R_{NTCL}}$$

Where R<sub>NTCH</sub> is the value of the NTC resistor at high temperature of the required temperature operation range, and R<sub>NTCL</sub> is the value of the NTC resistor at low temperature.

#### Resistor Choose for NTC Sensor for HOT PCB Temperature Monitor

ETA4662 features PCB temperature monitor function. When this function is set, Function will operate in both Charge and Discharge Mode and COLD detect is invalid. Same equations with Battery Temperature Monitor will be used normally.

#### **External Capacitor Selection**

Like most low-dropout regulators, the ETA4662 requires external capacitors for regulator stability and voltage spike immunity. The device is specifically designed for portable applications requiring minimum board space and smallest components, these capacitors must be correctly selected for good performance.

#### Input Capacitor

An input capacitor is required for stability, at least, a 1µF capacitor has to be connected between IN to GND for stable operation over full load current range. Basically, it is OK to have more output capacitance than input, as long as the input is at least 1µF.

#### Output Capacitor

This device is designed specifically to work with a very small ceramic output capacitor. A ceramic capacitor (dielectric types X5R or X7R) >2.2 $\mu$ F is suitable in the ETA4662 application circuit. For this device, the output capacitor should be connected between VSYS pin and GND pin with thick trace and small loop area.

### BAT to GND Capacitor

The capacitor from the BAT pin to GND pin is also necessary for ETA4662. A ceramic capacitor (dielectric types X5R or X7R) >2.2µF is suitable for the ETA4662 application circuit.

## VDD to GND Capacitor

The capacitor between VDD and GND is used to stabilize the VDD voltage to power the internal control and logic circuit. The typical value of this capacitor is 100nF.

### PCB Layout Guideline

Put external capacitors as close to this device as possible to make sure the smallest input inductance and the ground impedance. The PCB trace to connect the capacitor between VDD and GND is very important, and it should be put very close to this device.

The GND for the I<sup>2</sup>C wire should be clean, and it should not be very close to the GND. I<sup>2</sup>C wire should be put in parallel.

## **EVALUATION KIT DESIGN**

#### Table 4: ETA4662 EVKIT BOM List

| QTY | DEVICE  | VALUE | DESCRIPTION                        | PACKAGE | RECOMMENDED<br>MANUFATURE |

|-----|---------|-------|------------------------------------|---------|---------------------------|

| 1   | C1      | 1µF   | 20V Ceramic Capacitor (X5R or X7R) | 0603    | TBD                       |

| 2   | C2, C4  | 2.2µF | 10V Ceramic Capacitor (X5R or X7R) | 0603    | TBD                       |

| 2   | C3, C5  | 4.7µF | 10V Ceramic Capacitor (X5R or X7R) | 0603    | TBD                       |

| 1   | C6      | 100nF | 10V Ceramic Capacitor (X5R or X7R) | 0603    | TBD                       |

| 4   | R1, R2, | 15kΩ  | Resistor                           | 0603    | TBD                       |

| 4   | R3, R4  | 10812 |                                    | 0003    | עסו                       |

| 1   | PB      |       | Push Button                        |         | TBD                       |

## **I<sup>2</sup>C REGISTER MAP**

I<sup>2</sup>C Address is set 0ExH as default and can be programmable after power up by change ADDR[2:0] bits.

| REGISTER NAME ADDRESS RD/WR |      |                                            | DESCRIPTION                                                       | DEFAULT   |

|-----------------------------|------|--------------------------------------------|-------------------------------------------------------------------|-----------|

| REG00                       | 00xH | RD/WR                                      | Input Source Control Register                                     | 1001 1111 |

| REG01                       | 01xH | RD/WR                                      | Power on configuration register                                   | 1010 1100 |

| REG02                       | 02xH | RD/WR                                      | Charge Current Control Register                                   | 0000 1111 |

| REG03                       | 03xH | 03xH RD/WR Dis-charge/ Termination Current |                                                                   | 1001 0001 |

| REG04                       | 04xH | RD/WR                                      | Charge Voltage Control Register                                   | 1010 0011 |

| REG05                       | 05xH | RD/WR                                      | Charge Termination/Timer Control Register                         | 0111 1010 |

| REG06                       | 06xH | RD/WR                                      | Miscellaneous Operation Control Register                          | 1100 0000 |

| REG07                       | 07xH | RD/WR                                      | System Voltage Regulation Register                                | 0011 0111 |

| REG08                       | 08xH | RD                                         | System Status Register                                            | 0000 0000 |

| REG09                       | 09xH | RD                                         | Fault Register                                                    | 0000 0000 |

| REG0A                       | 0AxH | RD/WR                                      | I <sup>2</sup> C Address and Miscellaneous Configuration Register | 1110 0000 |

| REG0B                       | 0BxH | RD                                         | Device ID Register                                                | 0000 0000 |

# Table 5: Persister General Description

Table 6: Input Source Control Register - Memory Location: 00xH. Reset State: 1001 1111

| BIT | NAME              | POR | RESET BY | RD/WR | FUNCTION | NOTE                 |

|-----|-------------------|-----|----------|-------|----------|----------------------|

| 7   |                   | 1   | REG_RST  | RD/WR | 640mV    | Range: 3.88V – 5.08V |

| 6   | V/                | 0   | REG_RST  | RD/WR | 320mV    | Default:4.6V(1001)   |

| 5   | VINDPM[3:0]       | 0   | REG_RST  | RD/WR | 160mV    | Offset:3.88V         |

| 4   |                   | 1   | REG_RST  | RD/WR | 80mV     |                      |

| 3   |                   | 1   | REG_RST  | RD/WR | 240mA    | Range: 50mA – 500mA  |

| 2   | 10,01             | 1   | REG_RST  | RD/WR | 120mA    | Default:500mA(1111)  |

| 1   | -<br>Iin_lim[3:0] | 1   | REG_RST  | RD/WR | 60mA     | Offset:50mA          |

| 0   |                   | 1   | REG_RST  | RD/WR | 30mA     |                      |

#### Table 7: Power On Configuration Register - Memory Location: 01xH. Reset State: 1010 1100

| BIT  | NAME          | POR    | RESET BY | RD/WR   | FUNCTION           | NOTE                              |

|------|---------------|--------|----------|---------|--------------------|-----------------------------------|

| 7    |               | 1      | REG_RST  |         | 00: 8s             |                                   |

| 7    | T [1,0]       | 1      | WD_RST   | RD/WR   | 01: 12s            | Pull INT low time period to       |

| 6    | TRST_DGL[1:0] | 0      | REG_RST  | סויאים  | 10: 16s (Default)  | disconnect the battery.           |

| 6    | 0             | WD_RST | RD/WR    | 11: 20s |                    |                                   |

| 5    | T             | 1      | REG_RST  | RD/WR   | 0: 2s              | The QBYPASS and QSWITCH Lasts Off |

| 5    | Trst_dur      | I      | WD_RST   | RD/WR   | 1: 4s (Default)    | Time Before Auto-On               |

| 4    | EN HIZ        | 0      | REG_RST  | סויאס   | 0: Enabled         | Default: Enable(0)                |

| 4    | בוא_חוב       | U      | WD_RST   | RD/WR   | 1: Disabled        |                                   |

| 2    | CEB           | 1      | REG_RST  | RD/WR   | 0: Charge Enable   | Default:                          |

| 3 CE | VED           |        | WD_RST   |         | 1: Charge Disabled | Charge Disable(1)                 |

| 2 | VBAT_UVL0[2:0] | 1 | REG_RST<br>WD_RST | RD/WR | 360mV | Battery UVLO Threshold:                   |

|---|----------------|---|-------------------|-------|-------|-------------------------------------------|

| 1 |                | 0 | REG_RST<br>WD_RST | RD/WR | 180mV | Range: 2.4V – 3.03V<br>Default:2.76V(100) |

| 0 |                | 0 | REG_RST<br>WD_RST | RD/WR | 90mV  | Offset:2.4V                               |

#### Table 8: Charge Current Control Register - Memory Location: 02xH. Reset State: 0000 1111

| BIT | NAME      | POR | RESET BY            | RD/WR      | FUNCTION                               | NOTE                                                                                                                                                        |

|-----|-----------|-----|---------------------|------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | REG_RESET | 0   | REG_RST             | RD/WR      | 0: Keep current<br>setting<br>1: Reset | Once write REG_RST[] = 1, longer than<br>10ms needed before write REG_RST[] =<br>0. In the time between these 2 actions, can<br>write or read anything else |

| 6   | WD_RESET  | 0   | REG_RST             | RD/WR      | 0: Normal                              | Default: Normal(0)                                                                                                                                          |

|     |           |     | WD_RST              |            | 1: Reset                               |                                                                                                                                                             |

| 5   |           | 0   | REG_RST             | RD/WR      | 256mA                                  |                                                                                                                                                             |

| 0   |           | Ū   | WD_RST              |            |                                        |                                                                                                                                                             |

| 4   |           | 0   | REG_RST             | RD/WR      | 109m                                   |                                                                                                                                                             |

| 4   |           | 0   | WD_RST              |            | 128mA                                  |                                                                                                                                                             |

| 3   |           | 4   | REG_RST             | RD/WR 64mA | C 4mp A                                | Fast Charge Current setting:                                                                                                                                |

| 3   |           |     | WD_RST              |            | Range:8mA-456mA(111000)                |                                                                                                                                                             |

| 0   | Існд      |     | REG_RST             |            | 204                                    | Default:128mA(001111)                                                                                                                                       |

| 2   |           | 1   | WD_RST              | RD/WR      | 32mA                                   | Offset:8mA                                                                                                                                                  |

|     |           |     | REG_RST             |            | 10                                     |                                                                                                                                                             |

| Ί   |           | 1   | 1 WD_RST RD/WR 16mA |            | TomA                                   |                                                                                                                                                             |

| 0   |           |     | REG_RST             |            |                                        | ITIONC                                                                                                                                                      |

| U   | 0         | 1   | WD_RST              | RD/WR      | 8mA                                    |                                                                                                                                                             |

#### Table 9: Dis-charge/ Termination Current Register - Memory Location: 03xH. Reset State: 1001 0001

| J.          |      |                                   | J                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                  |  |  |

|-------------|------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME        | POR  | RESET BY                          | RD/WR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | NOTE                                                                                                                                                                                                                                                                                                                             |  |  |

|             | 1    | REG_RST                           | RD/WR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1600mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | BAT to SYS Discharge Current Limit                                                                                                                                                                                                                                                                                               |  |  |

| _           |      | WD_RST                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                  |  |  |

| 6           | 0    | REG_RST                           | RD/WR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 800mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Configuration:                                                                                                                                                                                                                                                                                                                   |  |  |

| lpaque[3:0] | 0    | WD_RST                            | D_RST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Range: 400mA – 3.2A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                  |  |  |

| 5           | -    | REG_RST                           | RD/WR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 400mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Default:2A(1001)<br>Offset:200mA                                                                                                                                                                                                                                                                                                 |  |  |

|             | 0    | WD_RST                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                  |  |  |