# Programmable Single Cell Li-Ion Battery Charger with Power

## Path Management

#### DESCRIPTION

The ETA4098 is a flexibly programmable highlyintegrated single cell Li-Ion and Li-polymer battery charger with power path management. It features pre-charging, fast charging(CC) and constant voltage(CV) charging, end-of charging termination, and auto-recharge. The built-in safe-timer monitors input voltage, input current, chip temperature, external temperature and load current, preventing from being damaged due to excessive high current and over-discharging. The charge current and charge termination current are programmable by flexible external resistors.

The power path management function features a low dropout regulator from the input to the system and a low Rdson switch from the battery to the system, ensuring the continuous power supply to the system.

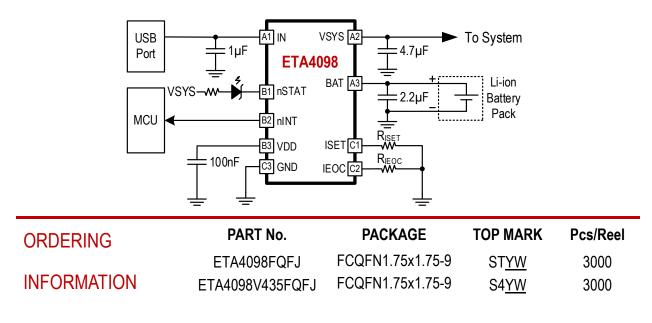

ETA4098 is available in a FCQFN-9L package.

### FEATURES

- Fully Autonomous Charger for Single Cell Li-Ion and Li-Polymer Battery

- 4.2/4.35V Charge Termination Voltage

- 21V Maximum Input Voltage Rating with Over-Voltage Protection

- ±0.5% Charging Voltage Accuracy

- Fully Integrated Power Switches and No External Blocking Diode Required

- Built-In Robust Charging Protection

- System Reset Function

- Built-In Battery Disconnection Function

- Thermal Limiting Regulation on Chip

- FCQFN-9L 1.75mmx1.75mm

#### **APPLICATIONS**

- Wearable Devices

- IoT Gadgets

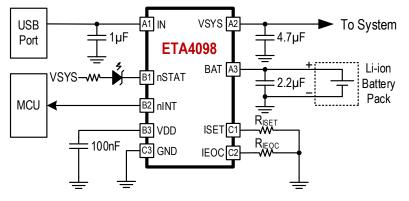

#### TYPICAL APPLICATION

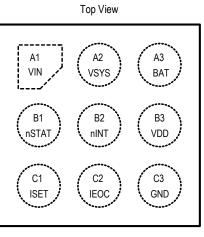

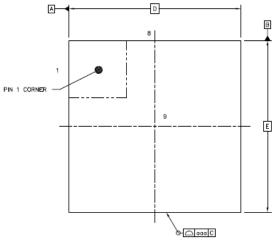

#### PIN CONFIGURATION

FCQFN1.75x1.75-9L

#### ABSOLUTE MAXIMUM RATINGS

(Note: Exceeding these limits may damage the device. Exposure to absolute maximum rating conditions for long periods may affect device reliability.)

| VIN Pin Voltage to GND0.3V to 28V              |

|------------------------------------------------|

| VIN to GND Discharge Current5mA                |

| VSYS to GND Voltage0.3V to 5.5V                |

| BAT Pins Voltage to GND1V to 6V                |

| All Other Pins Voltage to GND0.3V to 6V        |

| VSYS, BAT to ground current Internally limited |

| Operating Temperature Range40°C to 85°C        |

| Storage Temperature Range–55°C to 150°C        |

| Thermal Resistance $\theta_{JC}$ $\theta_{JA}$ |

| FCQFN-912                                      |

| Lead Temperature (Soldering, 10 seconds) 260°C |

| ESD HBM (Human Body Mode) 2KV                  |

| ESD MM (Machine Mode)200V                      |

#### ELECTRICAL CHARACTERISTICS

(V<sub>IN</sub> =5V, V<sub>BAT</sub>=4.2V unless otherwise specified. Typical values are at TA = 25°C.)

|                        | PARAMETER                                      | TESTCONDITIONS                                  | MIN  | TYP  | MAX       | UNIT |

|------------------------|------------------------------------------------|-------------------------------------------------|------|------|-----------|------|

| VIN INPUT AN           | ID BATTERY CONDITION                           |                                                 |      |      |           |      |

| V <sub>IN_UVLO</sub>   | VIN Input Under Voltage<br>Lock Out Threshold  | V <sub>IN</sub> Falling                         | 3.63 | 3.73 | 3.83      | V    |

| VIN_UVLO_HYS           | VIN_UVLO Hysteresis                            | V <sub>IN</sub> Rising                          |      | 170  | $ \zeta $ | mV   |

| V <sub>IN_OVP</sub>    | VIN Input Over Voltage<br>Protection Threshold | V <sub>IN</sub> Rising                          | 18.5 | 19   | 19.5      | V    |

| VIN_OVP_HYS            | VIN_OVP Hysteresis                             | V <sub>IN</sub> Falling                         |      | 500  |           | mV   |

| $V_{\text{IN\_CLAMP}}$ | VIN Input Clamp Voltage                        | Test for having 1mA clamp current.              | p 20 |      | V         |      |

| Ivin_shunt             | VIN Input Discharge<br>Current                 | V <sub>IN</sub> = 21V                           | 5    |      | mA        |      |

| V <sub>HDRM</sub>      | Sleep-Mode Entry<br>Threshold, VIN - VBAT      | V <sub>IN</sub> Falling vs. V <sub>BAT</sub> 85 |      |      | mV        |      |

| V <sub>HDRM_EXIT</sub> | Sleep-Mode Exit<br>Hysteresis                  | V <sub>IN</sub> Rising vs. V <sub>BAT</sub>     | 100  | 130  | 160       | mV   |

| V <sub>BAT</sub>       | BAT Input Voltage Range                        |                                                 |      |      | 5         | V    |

| tını                   | Input Detection Deglitch<br>Time               | For either under-voltage or over-voltage        |      | 250  |           | μs   |

|                                                      | PARAMETER                                       | TESTCONDITIONS                                                                    | MIN            | ТҮР  | MAX  | UNIT |

|------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------|----------------|------|------|------|

| tpwd                                                 | Input Power Detection<br>Time                   | Time before reporting power on or off                                             | g 50 75        |      | 100  | ms   |

| nINT Output Pulse<br>t <sub>INT_PULSE</sub> Duration |                                                 |                                                                                   |                | 250  |      | μs   |

| VBAT_UVLO                                            | Battery Under Voltage<br>Lockout Threshold      | V <sub>BAT</sub> Falling                                                          | 2.3            | 2.4  | 2.5  | V    |

| Vbat_uvlo_hys                                        | VBAT_UVLO Hysteresis                            | V <sub>BAT</sub> Falling,<br>V <sub>BAT_UVLO</sub> =2.76V                         |                | 210  |      | mV   |

| V <sub>BAT_OVP</sub>                                 | Battery Over Voltage<br>Protection Threshold    | V <sub>BAT</sub> Rising,<br>higher than V <sub>TERM</sub>                         |                | 130  |      | mV   |

| VBAT_OVP_HYS                                         | VBAT_OVP Hysteresis                             | V <sub>BAT</sub> Falling                                                          |                | 70   |      | mV   |

| IBAT_DSCHGOVP                                        | Battery Over-Voltage<br>Discharge               | 5                                                                                 |                |      | μA   |      |

| SUPPLY CUR                                           | RENT CONDITION                                  |                                                                                   |                |      |      |      |

| I <sub>Q_VIN</sub>                                   | Input Quiescent Current                         | V <sub>IN</sub> =5.5V, I <sub>CHG</sub> =0A,<br>I <sub>SYS</sub> = 0A             |                | 250  |      | μA   |

|                                                      |                                                 | V <sub>IN</sub> =5V, I <sub>SYS</sub> =0A,<br>Charge done, V <sub>BAT</sub> =4.3V |                | 5    |      |      |

| I <sub>Q_VBAT</sub>                                  | Battery Quiescent Current                       | V <sub>IN</sub> =GND, V <sub>BAT</sub> =4.35V,<br>I <sub>VSYS</sub> = 0A          | 12             |      |      | μA   |

| POWER PATH                                           | MANAGEMENT                                      | COLL                                                                              | ΤT             |      | IC.  |      |

| V <sub>SYS_REG</sub>                                 | Regulated System Output<br>Voltage Accuracy     | V <sub>IN</sub> = 5.5V, R <sub>VSYS</sub> =100Ω                                   | 4.50           | 4.55 | 4.60 | V    |

| Vsys_ovp                                             | System Over Voltage<br>Protection to Discharger | V <sub>SYS</sub> Rising,<br>As Percentage of V <sub>SYS_REG</sub>                 | 10             |      |      | %    |

| Vsys_ovp_hys                                         | V <sub>SYS_OVP</sub> Hysteresis                 | V <sub>SYS</sub> Falling,<br>As Percentage of V <sub>SYS_REG</sub>                | 5              |      | %    |      |

| Rvsys_dis                                            | V <sub>SYS</sub> Discharge<br>Resistance        | V <sub>SYS</sub> > V <sub>SYS_OVP</sub>                                           | 400            |      | Ω    |      |

| VINDPM                                               | Input Minimum Voltage<br>Regulation             |                                                                                   | 4.50 4.60 4.70 |      | 4.70 | V    |

| I <sub>IN_ILIM</sub>                                 | Input Current Limiting                          |                                                                                   | 440            | 470  | 500  | mA   |

| Ron_ldofet                                           | VIN to VSYS Switch On Resistance                | VIN=4.5V, IVSYS=100mA                                                             |                | 200  |      | mΩ   |

|                                                   | PARAMETER                                            | TEST                                              | CONDITIONS             | MIN            | ТҮР         | MAX            | UNIT |

|---------------------------------------------------|------------------------------------------------------|---------------------------------------------------|------------------------|----------------|-------------|----------------|------|

| R <sub>ON_BATFET</sub>                            | BATFET On Resistance                                 | V <sub>IN</sub> < 2V, V<br>I <sub>SYS</sub> =100n |                        | 100            |             | mΩ             |      |

| IBAT_LIM                                          | Battery Discharge Currrent<br>Limit                  |                                                   |                        | 2000           |             | mA             |      |

| Idischg_s                                         | Discharge Short Circuit<br>Limit                     |                                                   |                        |                | 3.7         |                | A    |

| I <sub>VIN_LOWSYS</sub>                           | Maximum VIN Current to<br>Shutoff                    | VSYS falli<br>V <sub>HSHORT</sub>                 | ng below               |                | 360         |                | mA   |

| V <sub>HSHORT</sub>                               | VSYS Short Detection<br>Threshold                    |                                                   |                        |                | 1.5         |                | V    |

| <b>t</b> CUTDEL                                   | Delay before Over Current<br>Cut                     |                                                   |                        |                | 60          |                | μs   |

| tRETRY                                            | Delay before Retry after<br>Cut                      |                                                   |                        |                | 800         |                | μs   |

| V <sub>FWD</sub>                                  | Ideal Diode Forward<br>Voltage in Supplement<br>Mode | 10mA Dis                                          | charge Current         |                | 20          |                | mV   |

| DYNAMIC POV                                       | VER MANAGEMENT AND BA                                | TTERY SU                                          | PPLEMENT               |                |             |                |      |

| DV <sub>SYS_LOW</sub>                             | SYS Drop for Lowering<br>Charging                    |                                                   |                        |                | 90          |                | mV   |

| DV <sub>IN_LOW</sub>                              | IN Drop for Lowering<br>Charging                     | S                                                 | SOLU.                  | TI             | 160         | IS.            | mV   |

| DV <sub>SYS-BAT_LOW</sub>                         | SYS-BAT Drop for<br>Supplement                       |                                                   |                        |                | 30          |                | mV   |

| DVsys-bat_reg                                     | SYS-BAT Regulation in<br>Supplement                  |                                                   |                        |                | 22.5        |                | mV   |

| $DV_{SYS\operatorname{-BAT}_\operatorname{HIGH}}$ | SYS-BAT drop for Exit<br>Supplement                  |                                                   |                        |                | 20          |                | mV   |

| BATFET RESE                                       | Т                                                    |                                                   |                        |                |             |                |      |

| t <sub>RST_DGL</sub>                              | Reset by nINT                                        |                                                   |                        |                | 8           |                | S    |

| t <sub>RST_DUR</sub>                              | BATFET Off Lasting Time                              |                                                   |                        |                | 2           |                | S    |

| BATTERY CHA                                       | RGER                                                 |                                                   |                        |                |             |                |      |

| V <sub>TERM</sub>                                 | Battery Charge<br>Termination Voltage                | I <sub>BAT</sub><br>= 1mA                         | ETA4098<br>ETA4098V435 | 4.179<br>4.329 | 4.2<br>4.35 | 4.221<br>4.371 | V    |

|                       | PARAMETER                                                             | TEST                                | CONDITIONS                             | MIN | TYP   | MAX | UNIT |

|-----------------------|-----------------------------------------------------------------------|-------------------------------------|----------------------------------------|-----|-------|-----|------|

|                       | Regulation (Aging and<br>pre-condition drift included<br>in 0°C~50°C) |                                     |                                        |     |       |     |      |

| V                     | ISET Pin Regulation                                                   | V <sub>BAT</sub> > V <sub>PI</sub>  | V <sub>BAT</sub> > V <sub>PRECHG</sub> |     | 0.8   |     | V    |

| V <sub>ISET</sub>     | Voltage                                                               | V <sub>BAT</sub> < V <sub>PI</sub>  | RECHG                                  |     | 0.25  |     |      |

| VIEOC                 | IEOC Pin Trip Threshold                                               |                                     |                                        |     | 0.25  |     | V    |

|                       |                                                                       | R <sub>ISET</sub> = 8k              | Ω                                      | 80  | 100   | 120 |      |

| I <sub>CHRG</sub>     | Fast Charge Current                                                   | R <sub>ISET</sub> = 3.2             | 2kΩ                                    | 220 | 250   | 280 | mA   |

|                       |                                                                       | R <sub>ISET</sub> = 2k              | Ω                                      | 360 | 400   | 440 |      |

| I <sub>PRE</sub>      | Pre-charge Current                                                    | $I_{PRE} = I_{TER}$                 | Μ                                      |     | ITERM |     | mA   |

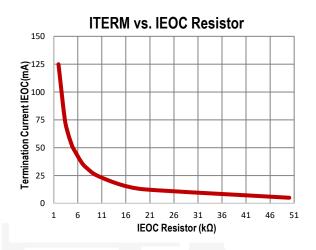

|                       | Chargo Termination                                                    | R <sub>IEOC</sub> = 20              | )kΩ                                    |     | 12.5  |     |      |

| I <sub>TERM</sub>     | Charge Termination<br>Current Threshold                               | R <sub>IEOC</sub> = 10              | )kΩ                                    |     | 25    |     | mA   |

|                       | R <sub>IEOC</sub> = 5                                                 |                                     | xΩ                                     |     | 50    |     |      |

| VPRECOND              | Precondition to Fast<br>Charge Threshold                              | Rising, V <sub>PRECOND</sub> = 3.0V |                                        | 2.9 | 3.0   | 3.1 | V    |

| VPRECOND_HYS          | Precondition to Fast<br>Charge Hysteresis                             | Falling                             |                                        |     | 90    |     | mV   |

| VRECH                 | Auto Recharge Voltage<br>Threshold                                    | Below VTE                           | ERM,                                   | 70  | 100   | 130 | mV   |

| t <sub>TERM_DGL</sub> | Termination Deglitch Time                                             |                                     |                                        |     | 200   |     | ms   |

| trech_dgl             | Battery Auto-Recharge<br>Deglitch Time                                | 5                                   | olu                                    | 200 |       | S   | ms   |

| tSAFETY               | Fast Charge Safety Timer                                              |                                     |                                        |     | 5     |     | Hrs  |

| THERMAL PR            |                                                                       |                                     |                                        | •   |       |     |      |

| $T_{J_REG}$           | Junction Temperature 120                                              |                                     |                                        | °C  |       |     |      |

| T <sub>J_SHDN</sub>   | Thermal Shutdown<br>Threshold                                         |                                     |                                        | 150 |       |     | °C   |

| Tj_shdn_hyst          | Thermal Shutdown<br>Hysteresis                                        |                                     | 20                                     |     |       | °C  |      |

| LOGIC IO PIN          | SPECIFICATION, nINT, SCL,                                             | SDA                                 |                                        |     |       |     | •    |

| VIL                   | Input Low Logic Voltage<br>Threshold                                  | Falling                             |                                        |     |       | 0.4 | V    |

| VIH                   | Input High Logic Voltage                                              | Rising                              |                                        | 1.3 |       |     | V    |

|     | PARAMETER        | TESTCONDITIONS          | MIN | TYP | MAX | UNIT |

|-----|------------------|-------------------------|-----|-----|-----|------|

| _   | Threshold        |                         |     |     |     |      |

| Vol | Output Low Level | I <sub>SINK</sub> = 5mA |     |     | 0.4 | V    |

NOTE: For lowering the bias current in the chip, and also to avoid biasing external circuit with output of nINT, the logic high level of the nINT should be an buffered level of an internal reference in range of 1.8~2.5V, at a roughly regulated voltage level.

#### PIN DESCRIPTION

| PIN# | PIN<br>NAME | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                         |

|------|-------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C2   | IEOC        | AIO  | Termination Charge Current Configuration Input Pin. Bypass a resistor to GND to set up termination threshold.                                                                                                                                                                                                       |

| C1   | ISET        | AIO  | Charge Current Configuration Input Pin. Bypass a resistor to GND to set up charge current. Bring ISET pin to a voltage greater than 1.1V to suspend charging.                                                                                                                                                       |

| B1   | nSTAT       | AIO  | Charge status pin. Pull low when charge in progress. Open drain for other conditions.                                                                                                                                                                                                                               |

| B2   | nINT        | AIO  | Interrupt Output and Battery FET Reset Input pin. The nINT pin sends charging status and fault notification to the host.<br>This pin is also used to reset the system from the battery. Refer to " <i>Interrupt to Host (nINT)</i> " and " <i>Battery Disconnection Function</i> " sections for detail information. |

| A1   | VIN         | Р    | Input Power Pin. Place a ceramic capacitor from IN pin to GND as close as possible to this device.                                                                                                                                                                                                                  |

| A2   | VSYS        | Р    | System Power Supply. Place a ceramic capacitor from SYS pin to GND as close as possible to this device.                                                                                                                                                                                                             |

| A3   | BAT         | Р    | Battery Pin. Place a ceramic capacitor from BAT pin to GND as close as possible to IC.                                                                                                                                                                                                                              |

| B3   | VDD         | Р    | Internal Control Power Supply Pin. Connect a 0.1µF ceramic cap from this pin to GND.                                                                                                                                                                                                                                |

| C3   | GND         | Р    | Ground Pin                                                                                                                                                                                                                                                                                                          |

| NA   | EP          | Р    | Thermal Pad. Connect to GND on PCB.                                                                                                                                                                                                                                                                                 |

Note: AIO = Analog Input and Output; DI = Digital Input; DO = Digital Output; DIO = Digital Input and Output; P = Power.

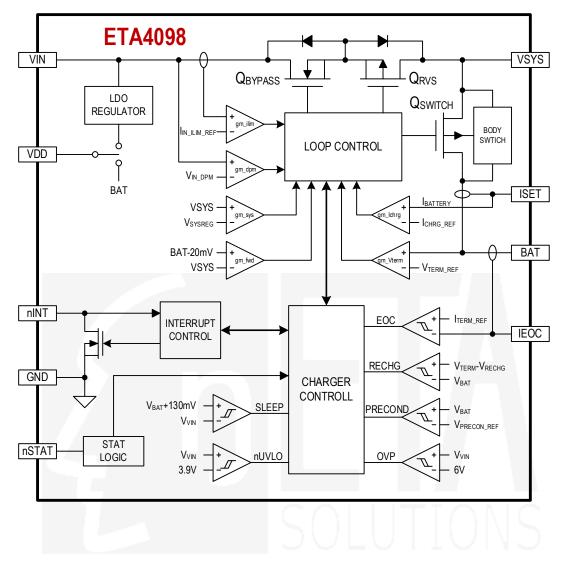

#### FUNCTIONAL BLOCK DIAGRAM

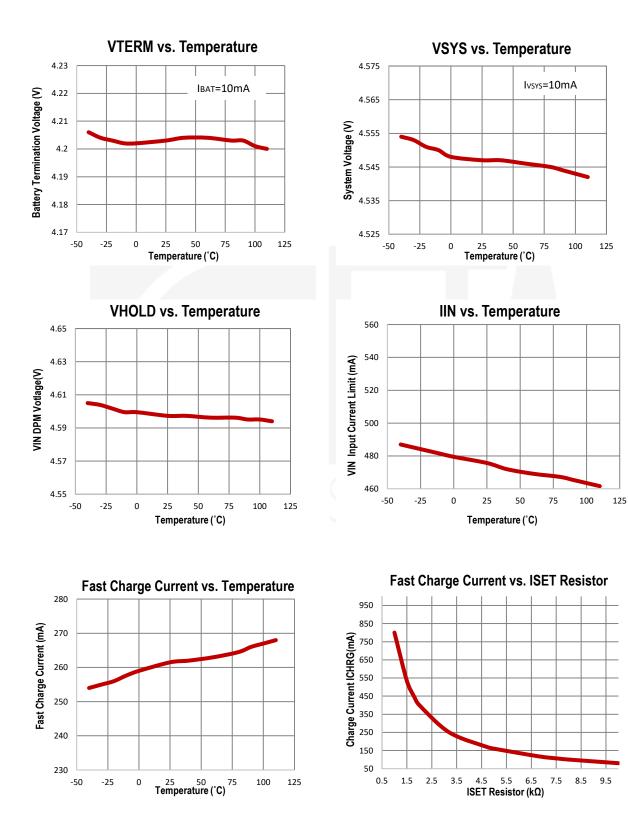

#### TYPICAL PERFORMANCE CHARACTERISTICS

(V<sub>IN</sub> =5V, V<sub>BAT</sub>=4.2V unless otherwise specified. Typical values are at TA = 25°C.)

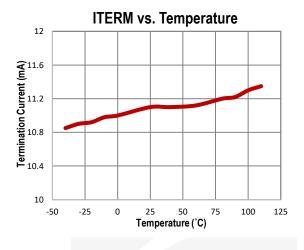

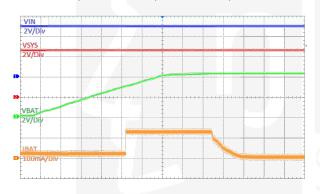

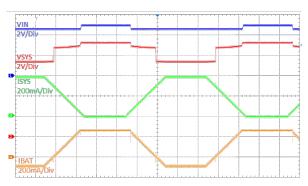

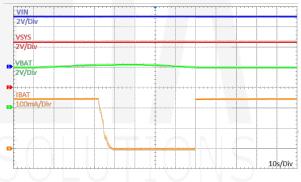

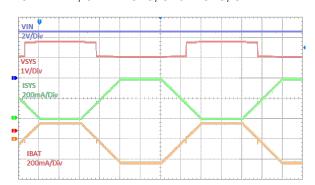

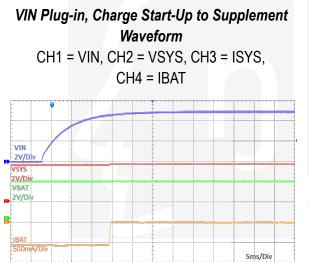

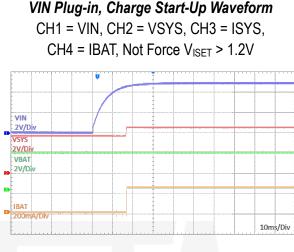

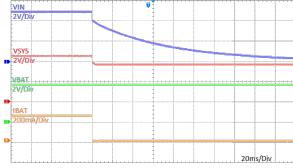

#### TYPICAL PERFORMANCE CHARACTERISTICS CONT'D

(V<sub>IN</sub> =5V, V<sub>BAT</sub>=4.2V unless otherwise specified. Typical values are at TA = 25°C.)

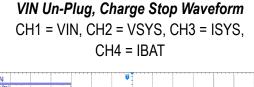

Charging Profile Curve CH1 = VIN, CH2 = VSYS, CH3 = VBAT, CH4 = IBAT

*Minimum Input voltage regulation based PPM* CH1 = VIN, CH2 = VSYS, CH3 = ISYS, CH4 = IBAT

**Recharging Profile Curve** CH1 = VIN, CH2 = VSYS, CH3 = VBAT, CH4 = IBAT

*Minimum Input voltage regulation based PPM* CH1 = VIN, CH2 = VSYS, CH3 = ISYS, CH4 = IBAT

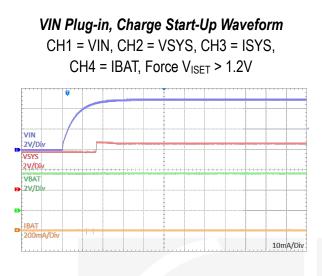

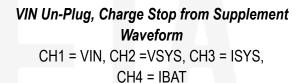

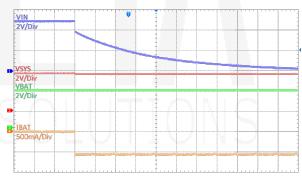

#### TYPICAL PERFORMANCE CHARACTERISTICS CONT'D

(V\_IN =5V, V\_BAT=4.2V unless otherwise specified. Typical values are at TA =  $25^{\circ}$ C.)

**Battery Removal** CH1 = VIN, CH2 = VSYS, CH3 = ISYS, CH4 = IBAT

www.etasolution.com

#### OPERATION

#### **General Description**

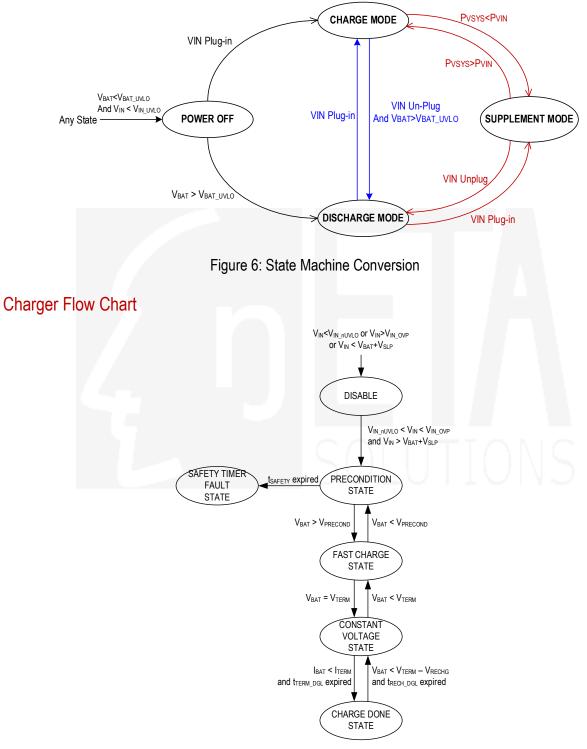

The ETA4098 is a single cell battery charger with power path management function for Li-Ion and Li-Polymer battery. It features pre-charging, fast charging (CC) and constant voltage (CV) charging, end-of charging termination, and auto-recharge.

A bypass FET between IN and SYS pins, and a battery switch FET between SYS and BAT pins are integrated for providing complete power path management. System load is prior in getting power from the input or is switched to battery power when the input is weak or is removed. Power to the battery is regulated by the battery switch FET during charging, while the input voltage, input current, voltage to system load, chip temperature.

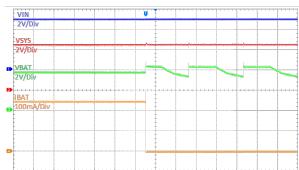

*Figure 1:* shows the power paths and key circuit blocks in the ETA4098, where the Qbypass regulates voltage to the system load and to the circuit for charging, the Qrvs prevents reverse leakage from the SYS node to IN node and the Qswitch regulates for charging or gates the discharging from the BAT node to SYS node. The charging circuit and the discharging have their own UVLO and bias, and the common circuit is powered by the higher voltage of the IN node or SYS node. The I/F is ready whenever any power is available.

Figure 1: Power Path Management Structure

#### Input Detection

The device monitors the input at the IN node. When the input is within the normal range certified by the UVLO circuit and OVP circuit for more than  $t_{INI}$  the charge circuit starts. The circuit stops or turns into OVP cut off instantly when the input voltage is lower than VIN\_UVLO or is higher than VIN\_OVLO, that the Qbypass and Qrvs are turned open.

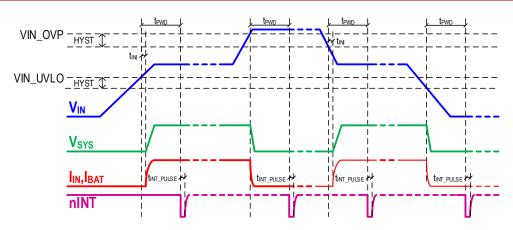

*Figure 2*: shows the timings relative to the input detection. The input state is certified after  $t_{INI}$  and stays for over  $t_{PWD}$ , the device outputs a pulse through the nINT. The nINT is internally pulled up to an unregulated reference voltage unless the battery is set into disconnected state. The nINT asserts pulse whenever an effective input change is certified, while the changes occurring within  $t_{PWM}$  do not assert pulse.

Figure 2: Input Power Detection and Operation Timings

#### Power Path Management

When the input is available ( $V_{IN} > V_{IN\_UVLO}$ ,  $V_{IN} - V_{SYS} > V_{HDRM}$ ), the device intends to power the system load with input by regulating the input voltage to  $V_{SYS\_REG}$  ( $V_{SYS}$  is decided by the input voltage, input current limit and battery voltage in reality).

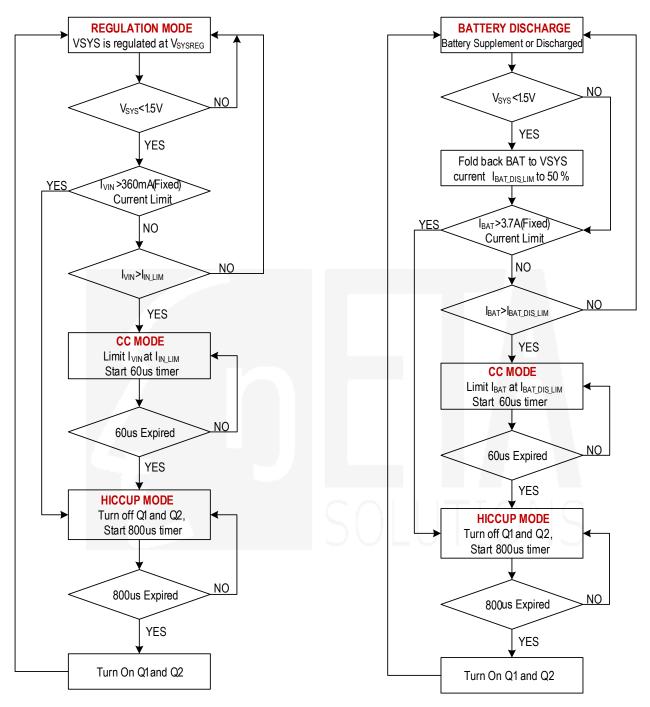

#### **Battery Charge Profile**

T

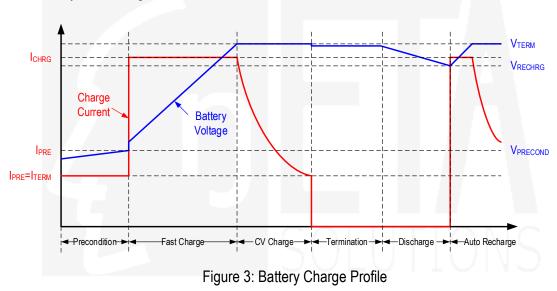

The charging profile managed by the device is as shown in *Figure 3*, which is segmented as following phases:

*Pre-charge:* If the battery voltage is less than the pre-charging threshold V<sub>BAT\_PRE</sub>, it charges the battery with pre-charging current, which shares the same value of the termination current programmed by IEOC resistor.

**Constant-Current Charge:** When battery voltage is higher than V<sub>BAT\_PRE</sub>, and is less than V<sub>BAT\_REG</sub>, it is charged with constant current that is programmed by the resistor connected to GND from ISET pin.

| ISET RESISTOR (kΩ) | CHARGE CURRENT (mA) |

|--------------------|---------------------|

| 1                  | 800                 |

| 1.5                | 533.3333            |

| 1.8                | 444.4444            |

| 2                  | 400                 |

| 3.2                | 250                 |

| 4.7                | 170.2128            |

| 5                  | 160                 |

| 8                  | 100                 |

| 10                 | 80                  |

| able 1. | Charge | Current       | Configura | ation by | ISET | Resistor |

|---------|--------|---------------|-----------|----------|------|----------|

|         | ena ge | • • • • • • • | oomgan    |          |      |          |

**Constant-Voltage Charge:** When the battery voltage rises close to the battery voltage V<sub>BAT\_REG</sub> = 4.2V, the charge current begins to decreases until the termination situation is identified.

During the whole charging process, the actual charge current may be less than the register setting due to other loop regulations like dynamic power management (DPM) regulation (input voltage, input current), or thermal regulation.

| irrent Configuration by IEOC Resisto |

|--------------------------------------|

| TERMINATION CHARGE<br>THRESHOLD (mA) |

| 125                                  |

| 62.5                                 |

| 50                                   |

| 31.25                                |

| 25                                   |

| 12.5                                 |

| 5                                    |

|                                      |

A new charge cycle starts when the following conditions are valid:

- The input power is recycled, or

- Auto-recharge kicks in.

Under the following conditions:

No battery over voltage event.

#### Battery Over-Voltage Protection

This device is designed with a built-in battery over-voltage limit about V<sub>BAT OVP</sub> higher than the V<sub>BAT REG</sub>. When the battery over-voltage event occurs, the device immediately suspends the charging and asserts a fault. A discharging path is turned on when the battery OVP keeps.

#### Input Current and Input Voltage Based Power Management

To meet the input source (USB usually) maximum current limit specification, the IC features the input current based power management by continuously monitoring the input current. The total input current limit is fixed at 500mA prevent the input source from over-loaded.

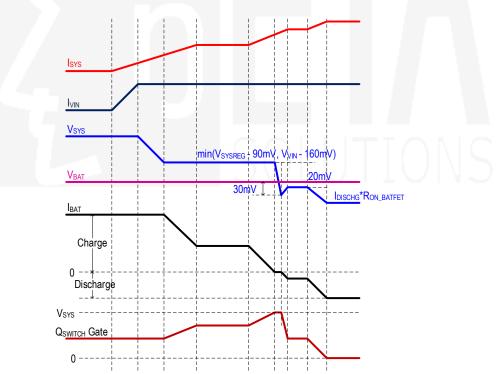

If the preset input current limit is higher than the rating of the input source, the back-up input voltage based power management also works to prevent the input source from being over-loaded. Either the input current limit or the input voltage limit is reached, the Qbypass between IN and SYS pins will be regulated so that the

total input power will be limited. As a result the system voltage drops, once the system declines to minimum value of the  $V_{SYS\_REG}$  -  $D_{VSYS\_LOW}$  and  $V_{IN}$  -  $D_{VIN\_LOW}$ , the charge current will be reduced to prevent the system voltage from dropping further.

The voltage based dynamic power management (DPM) will regulate the input voltage to  $V_{IN\_MIN}$  when the load is over the input power capacity.

The  $V_{IN\_MIN}$  is fixed at 4.6V.

#### Battery Supplement Mode

As mentioned above, the charge current is reduced to keep the input current or input voltage in regulation when DPM happens. If the charge current is reduced to zero and the input source is still overloaded due to heavy system load, the system voltage starts to decrease. Once the system voltage falls  $D_{VSYS}$ -BAT\_LOW below the battery voltage, the device enters battery supplement mode and the ideal diode mode will be enabled. The Qswitch is regulated to maintain the  $V_{BAT}$  -  $V_{SYS}$  at  $D_{VSYS}$ - $V_{BAT_REG}$  when  $I_{DSCHG}$  (supplement current) ×  $R_{ON_BAT}$  is lower than  $D_{VSYS}$ - $V_{BAT_REG}$ , in the case the  $I_{DSCHG}$  ×  $R_{ON_BAT}$  is higher than  $D_{VSYS}$ - $V_{BAT_REG}$ , in the case the  $I_{DSCHG}$  ×  $R_{ON_BAT}$  is higher than  $D_{VSYS}$ - $V_{BAT_REG}$ , the Qswitch is fully turned on to keep ideal forward voltage. During system load decreasing, once  $V_{SYS}$  is higher than  $V_{BAT}$  +  $D_{VSYS}$ -BAT\_HIGH, the ideal diode mode will be disabled. Figure 4 shows the dynamic power management and battery supplement mode operation profile.

When VIN is not available, the device operates in discharge mode; the Qswitch is always fully on to reduce the loss.

Figure 4: Dynamic Power Management and Battery Supplement Operation Profile

#### **Battery Regulation Voltage**

The battery voltage for the constant voltage regulation phase is  $V_{BAT_REG}$ . When battery is float, the BAT pin voltage varies between  $V_{BAT_REG}$  -  $V_{RECH}$  and  $V_{BAT_REG}$ .

#### Thermal Regulation and Shutdown

The device continuously monitors the internal junction temperature to maximize power delivery and avoid overheating the chip. When the internal junction temperature reaches preset limit of T<sub>J\_REG</sub>, the device starts to reduce the charge current to prevent higher power dissipation

When the junction temperature reaches  $T_{J\_SHDN}$  that is slightly higher than most high programmable thermal regulation temperature threshold, both the Qbypass and Qswitch are turned off.

#### nSTAT Charging Status

#### Table 3. nSTAT Indication

| STATE                                                                           | nSTAT BEHAVIOUS                       |

|---------------------------------------------------------------------------------|---------------------------------------|

| - Precondition State, or<br>- Fast Charge State, or<br>- Constant Voltage State | nSTAT is pulled low.                  |

| - Charge Disable, or<br>- Charge Done State                                     | nSTAT is floating                     |

| - Charge Fault State                                                            | nSTAT is driven<br>ON(0.5s)/OFF(0.5s) |

#### Battery Discharge Function

If battery is connected and the input source is missing, the BETFET is fully on when  $V_{BAT}$  is above the  $V_{BAT_UVLO}$  threshold. The low Ron Qswitch minimizes the conduction loss during discharge. The quiescent current of the device is as low as  $6\mu$ A in this mode.

#### Over-Discharge Current Protection

The over-discharge current protection is effective in discharge mode and supplement mode. Once the  $I_{BAT}$  exceeds discharge current limit, fixed at 2A, the Qswitch cuts off after  $t_{DSCHG_CUT}$  and the device resumes conducting after  $t_{RETRY}$ . Besides, if the discharge current goes high to hit  $I_{DSCHG_S}$ , the Qswitch cuts off instantly.

When the battery voltage falls below V<sub>BAT\_UVLO</sub>, the Qswitch cuts off to prevent over discharge.

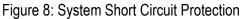

#### System Short Circuit Protection

When system short circuit occurs, the Qswitch cuts the BAT to VSYS path and the Qbypass limits the current input through the VIN to SYS path. If the system short circuit remains, the die temperature goes high to cause thermal shut down.

The ETA4098 features VSYS node short circuit protection for both VIN to VSYS path and BAT to VSYS path.

- VIN to VSYS path: The ETA4098 starts activate hard short protection after V<sub>SYS</sub> goes greater than 1.5V once. This means the IC allows to start-up with full current limit. Once this condition occurs, if V<sub>SYS</sub> falls below 1.5V, and I<sub>IN</sub> is found over the protection threshold, Q<sub>SWITCH</sub>, Q<sub>BYPASS</sub> and Q<sub>RVS</sub> are turned off immediately. And the operation of the IC goes into the hiccup mode. Beside hard short protection, at any time V<sub>SYS</sub> is lower than 1.5V, while the setting input current limit is reached, I<sub>IN</sub> is regulated at I<sub>IN\_LIM</sub> the hiccup mode also starts after a 60µs delay. The interval of the hiccup mode is 800us.

- BATT to SYS path: Once I<sub>BAT</sub> is found over the 3.7A protection threshold, both the LDO FET and the BATT FET are turned off immediately and the operation of the IC goes into the hiccup mode. Besides, while the battery discharge current limit threshold is reached, the hiccup mode also starts after a 60µs delay. The interval of the hiccup mode is 800us. For details, please refer to flow chart in Figure 7.

- Particularly, if the system short circuit happens when both input and battery are present, the protection mechanism of both paths will work, the faster one dominates the hiccup operation.

#### Interrupt to Host (INT)

This device also has an alert mechanism which can output an interrupt signal via nINT pin to notify the system on the operation by outputting low for t<sub>INT\_PULSE</sub>. Any of the events listed below triggers the nINT output.

- Good input source detected

- UVLO or input over voltage detected

- Charge completed

- Charging status change

- Any fault (input fault, battery OVP fault)

The nINT is pulled up to an unregulated low voltage that is not high enough to most logic circuit (in the circuit the device loads), to avoid unexpected creeping powering and leakage during power recycling and in shipping mode; the nINT is pulled up to a high voltage in other states. Both the low voltage and high voltage are internally generated and pull up is weak and could be over-driven externally.

#### **Battery Disconnection Function**

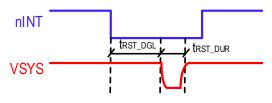

This device can also reuses nINT pin to cut off the path from battery to system under the condition need to recycle the system power. Once the logic at nINT pin set to low for more than  $t_{INT_OFF}$  which can be programmed via  $t_{RST_DGL}$ , the battery is disconnected from the system by turning off the Qswitch and Qbypass, the off state lasts for  $t_{INT_ON}$  which can be programmed via  $t_{RST_DUR}$ , then the Qswitch and Qbypass will be automatically turned on and system is powered again. During the off period, the nINT pin is biased to a lower voltage.

The waveforms of power recycling are shown in Figure 5.

Figure 5. Power Recycling Waveforms

#### **OPERATION DIAGRAM**

#### Main State Machine

#### System Short Circuit Protection

#### APPLICATION INFORMATION

#### Input Capacitor

An input capacitor is required for stability, at least, a  $1\mu$ F capacitor has to be connected between IN to GND for stable operation over full load current range. Basically, it is OK to have more output capacitance than input, as long as the input is at least  $1\mu$ F.

#### **Output Capacitor**

This device is designed specifically to work with a very small ceramic output capacitor. A ceramic capacitor (dielectric types X5R or X7R) >2.2 $\mu$ F is suitable in the ETA4098 application circuit. For this device, the output capacitor should be connected between VSYS pin and GND pin with thick trace and small loop area.

#### BAT to GND Capacitor

The capacitor from the BAT pin to GND pin is also necessary for ETA4098. A ceramic capacitor (dielectric types X5R or X7R) >2.2 $\mu$ F is suitable for the ETA4098 application circuit.

#### VDD to GND Capacitor

The capacitor between VDD and GND is used to stabilize the VDD voltage to power the internal control and logic circuit. The typical value of this capacitor is 100nF.

#### PCB Layout Guideline

Put external capacitors as close to this device as possible to make sure the smallest input inductance and the ground impedance.

The PCB trace to connect the capacitor between VDD and GND is very important, and it should be put very close to this device.

The GND for the I2C wire should be clean, and it should not be very close to the GND.

#### **EVALUATION KIT DESIGN**

Note: Pin# for QFNFC package

| Figure 9: ETA4098 | EVKIT Design |

|-------------------|--------------|

|-------------------|--------------|

| Table | 4: ETA4098 EVKIT E |       |                                       | · · · · |                           |

|-------|--------------------|-------|---------------------------------------|---------|---------------------------|

| QTY   | DEVICE             | VALUE | DESCRIPTION                           | PACKAGE | RECOMMENDED<br>MANUFATURE |

| 1     | C1                 | 1µF   | 20V Ceramic Capacitor<br>(X5R or X7R) | 0603    | TBD                       |

| 2     | C2, C4             | 2.2µF | 10V Ceramic Capacitor<br>(X5R or X7R) | 0603    | TBD                       |

| 2     | C3, C5             | 4.7µF | 10V Ceramic Capacitor<br>(X5R or X7R) | 0603    | TBD                       |

| 1     | C6                 | 100nF | 10V Ceramic Capacitor<br>(X5R or X7R) | 0603    | TBD                       |

| 4     | R1, R2, R3, R4     | 15kΩ  | Resistor                              | 0603    | TBD                       |

| 1     | PB                 |       | Push Button                           |         | TBD                       |

.

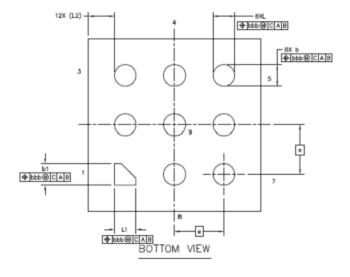

#### PACKAGE OUTLINE DIMENSIONS

#### Package: FCQFN-9L 1.75mmx1.75mm

| // ccc C |                         |

|----------|-------------------------|

|          |                         |

| _        |                         |

|          |                         |

|          | + A2 + + + A1<br>+ (A3) |

| S        | DE VIEW                 |

|                     |     | SYMBOL    | MIN      | NOM  | MAX  |

|---------------------|-----|-----------|----------|------|------|

| TOTAL THICKNESS     | A   | 0.32      | 0.37     | 0.4  |      |

| STAND OFF           | A1  | 0         | 0.02     | 0.05 |      |

| MOLD THICKNESS      | A2  |           | 0.27     |      |      |

| L/F THICKNESS       | A3  | 0.102 REF |          |      |      |

| LEAD WIDTH          |     | ь         | 0.17     | 0.22 | 0.27 |

| LEAD WIDTH          |     | Ь1        | 0.12     | 0.22 | 0.32 |

| BODY SIZE           | ×   | D         | 1.75 BSC |      |      |

| BOOT SIZE           | Y   | E         | 1.75 BSC |      |      |

| LEAD PITCH          | е   | 0.5 BSC   |          |      |      |

| LEAD LENGTH         |     | L         | 0.17     | 0.22 | 0.27 |

| LEAD LENGTH         | Ľ   | 0.12      | 0.22     | 0.32 |      |

| LEAD EDGE TO PACKAG | L2  | 0.265 REF |          |      |      |

| PACKAGE EDGE TOLERA | qqq | 0.1       |          |      |      |

| MOLD FLATNESS       | ccc | 0.1       |          |      |      |

| COPLANARITY         | eee | 0.05      |          |      |      |

| LEAD OFFSET         | bbb | 0.1       |          |      |      |

|                     |     |           |          |      |      |

|                     |     |           |          |      |      |

|                     |     |           |          |      |      |

|                     |     |           |          |      |      |